# General Standards Corporation

## High Performance Bus Interface Solutions

# **16AIO**

# 16-Bit Analog Input/Output Board With 32 Input Channels, 4 Output Channels and 16-Bit Digital I/O Port

Available in PMC, PCI, cPCI and PC104-Plus and PCI Express form factors as:

PMC66-16AIO: PMC, Single-width

PCI66-16AIO: PCI, short length

cPCI66-16AIO: cPCI, 3U

PCIe-16AIO: PCI Express

PCIe104-16AIO: PCIe, one-lane on PC/104 form factor

See Ordering Information for details. (The PC104-*Plus* version is available only in native format, and is supported by a dedicated PC104-*Plus* product specification) Call for the availability of other form factors, such as XMC, CCPMC, etc.

This specification applies primarily to the PMC form-factor.

#### Features Include:

- 32 Single-Ended or 16 Differential 16-Bit Scanned Analog Input Channels

- 4 Analog Output Channels, 16-Bit D/A Converter per Channel

- ±15mA Peak Output Load Capacity Available

- 16-Bit Bi-directional Digital Port with Two Auxiliary I/O Lines

- Software-Selectable Analog Input/Output Ranges of ±10V, ±5V or ±2.5V. Optional output ranges of 0 to +10V, 0 to +5V, 0 to +2.5V.

- Available also with 16 High-Level analog input channels, for monitoring high-level digital inputs. ±60V, ±30V, or ±15V; Configurable as 16 single-ended channels or 8 differential channels.

- Independent 32K-Sample Analog Input and Output FIFO Buffers□

- 300K Samples per Second Aggregate Analog Input Sample Rate

- Multiple-Channel and Single-Channel Input Scanning Modes

- Low Crosstalk, Noise and Input Bias Current; Buffer Amplifiers on all Analog Input Lines

- 300K Samples per Second per Channel Analog Output Clocking Rate (1200 KSPS Aggregate Rate)

- Supports Waveform and Arbitrary Function Generation; Continuous and One-shot Modes

- Internal Rate Generator Controls Input Sampling, Output Sampling, or Both Simultaneously

- Supports Multiboard Synchronization of Analog Inputs and Outputs

- Internal Auto calibration of Analog Input and Output Channels

- Continuous and Burst (One-Shot) Input and Output Modes

- DMA Engine Minimizes Host I/O Overhead

## Applications:

| □ Data Acquisition Systems                   | <ul> <li>Automatic Test Equipment</li> </ul> |

|----------------------------------------------|----------------------------------------------|

| □ Industrial Robotics                        | ☐ Function and Waveform Generation           |

| □ Precision Voltage Sourcing and Measurement | □ Research Instrumentation                   |

REV 011911

### Functional Description:

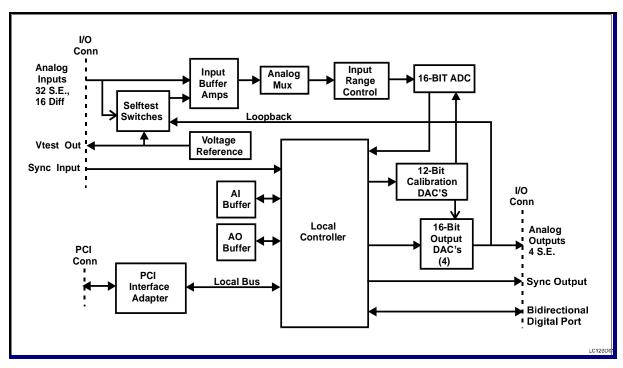

The 16AIO provides cost effective high-speed 16-bit analog input/output resources on a standard I/O module. Four analog output channels can be updated either synchronously or asynchronously, and support waveform generation. Internal autocalibration networks permit calibration to be performed without removing the board from the system. Software-controlled test configurations include a loopback mode for monitoring all analog output channels. Gain and offset correction of the analog input and output channels is performed by calibration DAC's that are loaded with channel correction values during autocalibration. For all form-factors except PC104-*Plus*, a digital I/O port provides 16 bidirectional data lines and two auxiliary I/O lines.

The analog inputs are software-configurable either as 32 single-ended channels or as 16 differential signal pairs. Buffer amplifiers on all input lines eliminate multiplexer input switching noise, and minimize crosstalk and input bias currents. Analog input data accumulates in a 32K-sample buffer until retrieved by the control bus. Each of the four analog output channels contains a dedicated 16-bit D/A converter and an output range control network. The board receives analog output data from the control bus through a 32K-sample FIFO buffer.

Figure 1. 16AIO; Functional Organization

The board is functionally compatible with the IEEE PCI local bus specification Revision 2.3, and supports the "plug-n-play" initialization concept. System input/output connections are made at the panel bracket through a high-density 68-pin connector. Power requirements consist of +5 VDC, in compliance with the PCI specification, and operation over the specified temperature range is achieved with conventional convection cooling.

#### **ELECTRICAL SPECIFICATIONS**

At +25 <sup>O</sup>C, with specified operating voltages

#### ANALOG INPUT CHANNELS

#### Input Characteristics:

Configuration: 32 input lines, configurable as 32 single-ended or 16 differential channels

Voltage Ranges: Software configurable as ±10, ±5 or ±2.5 Volts

Input Impedance: 1.0 Megohms line-to-ground, 2.0 Megohms line-to-line, in parallel with

100Pfd. Independent of scan rate. (180K ±20K Line-to ground for High-Level

inputs).

Bias Current: 80 nanoamps maximum

Signal to Noise (SNR): 80 dB typical

Common Mode Rejection: 60 dB typical, DC-60 Hz, differential input mode. (30dB for High-Level inputs).

Common Mode Range: ±10 Volts; differential input configuration. (±60 Volts for High-Level inputs).

Overvoltage Protection: Standard: ±30 Volts with power applied; ±15 Volts with power removed

(±70 Volts for High-Level inputs).

#### □ Transfer Characteristics:

Resolution: 16 Bits; 0.0015 percent of FSR

Maximum Conversion Rate: 300K conversions per second, minimum

Channels per scan: 2, 4, 8, 16, or 32 Channels per scan (32 channels available only in single-

ended mode)

Maximum Scan Rate: 75K scans per second in multiple-channel mode. 150 KSPS in 2-Channel

mode. 300KSPS in single-channel mode. Scan rate equals the conversion

rate divided by the number of channels per scan.

Minimum Scan Rate: 400 scans per second, using a single internal rate generator; 0.007SPS using

both generators. Zero, using a software sync flag or an externally supplied

sync input.

DC Accuracy: Standard Inputs:

(Maximum composite error, Range Midscale Accuracy ±Fullscale Accuracy referred to inputs) ±10V ±3.2mV ±4.2mV

±10V ±3.2mV ±4.2mV ±5V ±2.3mV ±2.8mV ±2.5V ±1.6mV ±2.0mV

**High-Level Inputs:**

Range Midscale Accuracy ±Fullscale Accuracy ±60V ±30mV (±6% of Range)

±30V ±17mV ±15V ±10mV

Crosstalk Rejection: 85dB, DC-10kHz

Integral Nonlinearity: ±0.003 percent of FSR, maximum

Differential Nonlinearity: ±0.0015 percent of FSR, maximum

#### Analog Input Operating Modes and Controls

Analog Input Modes: Single Scan: A software or hardware sync initiates a single scan of all

active channels at the maximum conversion rate. As many as three target boards can be synchronized to a single

initiator board.

Continuous Scan: Inputs are scanned continuously at the selected scan rate.

Selftest: Reference and loopback tests; autocalibration

Multiple-Channel: 4, 8, 16 or 32 channels per scan

Single-Channel: Any single channel can be selected for digitizing at the

maximum conversion rate.

Two-Channel: 2-Channel scan size.

Input Data Buffer: 32K-sample FIFO with 0000h-7FFEh adjustable threshold flag;

supported

#### **ANALOG OUTPUT CHANNELS**

#### Output Characteristics:

Configuration: Four single-ended output channels. (Ordering option)

Voltage Ranges: Same as selected for analog inputs; ±10, ±5 or ±2.5 Volts.

Optional output ranges of 0 to +10V, 0 to +5V, 0 to +2.5V.

Output Resistance: 1.0 Ohm, maximum

Output protection: Withstands sustained short-circuiting to ground

Load Current: Zero to ±3ma per individual channel. (Zero to ±15 peak-mA with high-current

output option. 40mA maximum RMS loading for all four outputs. See power

requirements pertaining to 15mA output loading).

Load Capacitance: Stable with zero to 2000 pF shunt capacitance

Noise: 1.0mV-RMS, 10Hz-1MHz typical

Glitch Impulse: 5 nV-Sec typical, ±2.5V range

#### Transfer Characteristics:

Resolution: 16 Bits (0.0015 percent of FSR)

Output Sample Rate: Software adjustable from 400SPS to 300KSPS per channel; 0.006SPS to

300KSPS using both internal rate generators. DC to 300KSPS with hardware

or software sync.

DC Accuracy: Range Midscale Accuracy ±Fullscale Accuracy

Range

Zero Accuracy

+Fullscale Accuracy

0 to +10V

±1.5mV

±2.5mV

0 to +5V

±1.0mV

±1.8mV

0 to +2.5V

±0.9mV

±1.5mV

Settling Time: 8us to 1LSB, typical with 50-percent fullscale step

Crosstalk Rejection: 85 dB minimum, DC-1000Hz

Integral Nonlinearity: ±0.004 percent of FSR, maximum

±0.0015 percent of FSR, maximum

DMA is

#### Analog Output Operating Modes and Controls

Clocking Modes: Simultaneous Continuous Mode: Channel values in a designated channel

group are stored in an intermediate buffer, and then are transferred to the output DAC's when an output clock occurs. The clock can be generated either by the internal rate generator, by a software flag, or by an external hardware trigger. As many as three target boards can be clock-synchronized

to a single initiator board.

Simultaneous Burst Mode: A single function (i.e.: burst) is initiated by a software or hardware sync. During a burst, channel values in a designated channel group are stored in a transfer buffer, and then are transferred to the output DAC's each time a clock pulse is generated by the internal rate generator. The burst terminates when a Burst End flag is encountered

Channel-Sequential Modes: Same as simultaneous modes, except each value in the data buffer is written immediately to the associated output DAC. The

group-end flag is ignored in this mode.

Channel Assignment: A 2-bit field in the output buffer assigns the associated data field to a specific

output channel.

Group End: A single bit in the output buffer indicates the last value in a channel group.

Burst End: A single bit in the output buffer indicates the last value in an output burst

sequence.

Output Data Buffer: 32K-sample FIFO with 0000h-7FFEh adjustable threshold flag; DMA is

supported

#### **RATE GENERATORS**

Analog outputs and inputs can be clocked from either of two independent rate generators, or both inputs and outputs can be synchronized to a single generator. Each rate generator uses a 16-bit adjustable frequency divider, and the two generators can be operated in series to provide very low clocking rates.

#### **DIGITAL I/O PORT**

(All form-factors except PC104-Plus):

The digital I/O port consists of 16 bidirectional data lines, one auxiliary input line and one auxiliary output line. An interrupt request can be generated in response to the auxiliary input. The data lines are organized as two data bytes, each of which can be configured independently as either an input or output byte. Standard TTL logic levels apply, with 8 ma source/sink capability per output line.

#### PCI INTERFACE

□ **Compatibility:** Conforms to PCI Specification 2.3, with D32 read/write transactions.

Supports "plug-n-play" initialization.

Provides one multifunction interrupt.

Supports DMA transfers as bus master.

#### MECHANICAL AND ENVIRONMENTAL SPECIFICATIONS

#### **Power Requirements:**

+5VDC ±0.2 VDC at 1.4 Amps, maximum, 0.9 Amps typical. (1.8 Amps maximum if all outputs are loaded to 15mA.)

#### **Mechanical Characteristics** (PMC form factor)

Height: 13.5 mm (0.53 in)

Depth: 143.75 mm (5.66 in)

Width: 74.0 mm (2.91 in)

#### **Environmental Specifications**

Ambient Temperature Range:

Standard Temperature: Operating: 0 to +70 Degrees Celsius \*

Storage: -40 to +85 Degrees Celsius

Extended Temperature: Operating: -40 to +80 Degrees Celsius \*

Storage: -40 to +85 Degrees Celsius

\* Air temperature at board surface.

Relative Humidity: 0 to 95%, non-condensing

Altitude: Operation to 10,000 ft.

Cooling: Conventional air cooling; 150 LFPM

#### ORDERING INFORMATION

Specify the basic product model number followed by an option suffix "-AB-C-D-E", as indicated below. For example, model number PMC-16AIO-41-15MA-BP-SCSI3 describes a PMC module with four output channels, a bezel and EMI shield, 15MA bipolar analog outputs, and a SCSI-3 I/O connector

| Basic Model Number      | Form Factor                          |  |

|-------------------------|--------------------------------------|--|

| PMC-16AIO               | PMC (Native)                         |  |

| PCI-16AIO <sup>1</sup>  | PCI, short length                    |  |

| PC104P-16AIO            | PC104-Plus (Native)                  |  |

| cPCI-16AIO <sup>1</sup> | cPCI, 3U                             |  |

| PCIe-16AIO 1            | cPCI, 3U                             |  |

| PCIe104-16AIO 1,2       | PCIe, one-lane on PC/104 form factor |  |

Module installed and tested on an adapter, with mechanical and functional equivalency. Contact factory for availability in native form factors.

<sup>&</sup>lt;sup>2</sup> PCIe104 supports only the PCIe bus.

| Optional Parameter       | Value                                           | Specify Option As:     |  |

|--------------------------|-------------------------------------------------|------------------------|--|

| Number of Analog Outputs | No Output Channels                              | A = 0                  |  |

|                          | 4 Output Channels                               | A = 4                  |  |

| EMI Shield               | No bezel or shield                              | B = 0                  |  |

| (Now standard)           | Bezel & shield installed                        | B = 1                  |  |

| Custom Features          | No Custom Features                              | C = 0                  |  |

|                          | 16 High-Level ±60V analog input channels        | C = 16HV60V            |  |

|                          | High-current analog outputs; ±15mA <sup>1</sup> | C = 15MA               |  |

| Software-Selectable      | Bipolar: ±10V, ±5V, ±2.5V                       | D = BP                 |  |

| Output Ranges            | Unipolar: 0 to +10V, 0 to +5V, 0 to +2.5V       | D = UP                 |  |

| System I/O Connector     | Robinson Nugent 68-Pin IDC                      | E = 0                  |  |

|                          | AMP 68-Pin SCSI-3 <sup>2</sup>                  | E = SCSI3 <sup>2</sup> |  |

<sup>&</sup>lt;sup>1</sup> Zero to ±15 peak-mA per output channel; 40 mA-RMS maximum total loading for all four outputs. If all outputs are loaded to 15mA, power consumption may exceed the maximum level recommended for PMC modules.

Native PMC form factor. Not currently available for PC104P; Contact factory if required for PC104P version

#### **SYSTEM I/O CONNECTIONS**

**Table 1. System Connector Pin Functions**

|     | ROW-A           | ROW-B |                 |

|-----|-----------------|-------|-----------------|

| PIN | SIGNAL *        | PIN   | SIGNAL          |

| 34  | ANA INP00 HI    | 34    | ANA OUT00       |

| 33  | ANA INP00 LO ** | 33    | OUTPUT RTN      |

| 32  | ANA INP02 HI    | 32    | ANA OUT01       |

| 31  | ANA INP02 LO    | 31    | OUTPUT RTN      |

| 30  | ANA INP04 HI    | 30    | ANA OUT02       |

| 29  | ANA INP04 LO    | 29    | OUTPUT RTN      |

| 28  | ANA INP06 HI    | 28    | ANA OUT03       |

| 27  | ANA INP06 LO    | 27    | OUTPUT RTN      |

| 26  | ANA INP08 HI    | 26    | VTEST           |

| 25  | ANA INP08 LO    | 25    | VTEST RTN       |

| 24  | ANA INP10 HI    | 24    | DIGITAL RTN     |

| 23  | ANA INP10 LO    | 23    | AUX DIGITAL IN  |

| 22  | ANA INP12 HI    | 22    | AUX DIGITAL OUT |

| 21  | ANA INP12 LO    | 21    | DIG IO 00       |

| 20  | ANA INP14 HI    | 20    | DIG IO 01       |

| 19  | ANA INP14 LO    | 19    | DIG IO 02       |

| 18  | INPUT RTN       | 18    | DIG IO 03       |

| 17  | INPUT RTN       | 17    | DIG IO 04       |

| 16  | ANA INP16 HI    | 16    | DIG IO 05       |

| 15  | ANA INP16 LO    | 15    | DIG IO 06       |

| 14  | ANA INP18 HI    | 14    | DIG IO 07       |

| 13  | ANA INP18 LO    | 13    | DIG IO 08       |

| 12  | ANA INP20 HI    | 12    | DIG IO 09       |

| 11  | ANA INP20 LO    | 11    | DIG IO 10       |

| 10  | ANA INP22 HI    | 10    | DIG IO 11       |

| 9   | ANA INP22 LO    | 9     | DIG IO 12       |

| 8   | ANA INP24 HI    | 8     | DIG IO 13       |

| 7   | ANA INP24 LO    | 7     | DIG IO 14       |

| 6   | ANA INP26 HI    | 6     | DIG IO 15       |

| 5   | ANA INP26 LO    | 5     | DIGITAL RTN     |

| 4   | ANA INP28 HI    | 4     | SYNC OUTPUT     |

| 3   | ANA INP28 LO    | 3     | DIGITAL RTN     |

| 2   | ANA INP30 HI    | 2     | SYNC INPUT      |

| 1   | ANA INP30 LO    | 1     | DIGITAL RTN     |

<sup>\*\*</sup> Analog inputs are shown for the differential input mode. In single-ended mode, LO inputs become consecutive odd-numbered channels, beginning with ANA INP 01 replacing ANA INP 00 LO, etc.

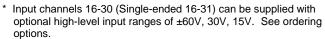

Figure 2. System Input/Output Connector

#### **System Mating Connector:**

#### **Robinson-Nugent Option:**

68-Pin 2-row 0.050" dual-ribbon cable socket connector: Robinson Nugent #P50E-068-S-TG, or equivalent.

#### **SCSI3 Option:**

68-pin 0.050" Subminiature connector with metal shield: AMP #749621-7 or equivalent.

General Standards Corporation assumes no responsibility for the use of any circuits in this product. No circuit patent licenses are implied. Information included herein supersedes previously published specifications on this product and is subject to change without notice.