# **General Standards Corporation**

High Performance Bus Interface Solutions

# PCIe-16A064C

# 16-Bit, 64/32-Channel, 500KSPS PCI Express Analog Output Board

## With Optional Outputs-Disconnect

#### Features Include:

- Precision 16-Bit simultaneously-clocked analog outputs: R-2R DAC per channel

- Available with either 64 single-ended outputs, or 32 balanced-differential outputs

- Software-selectable ranges of ±10V, ±5V. Optionally 0 to +10V, or 0 to +5V.

- Output clocking rates from zero to 500K samples per second per channel.

- Optional Outputs-Disconnect feature supports multiple-board redundancy, and eliminates outputs activity during autocalibration

- Remote ground-sense input minimizes the effects of interground potentials

- Supports Block-mode and Demand-mode DMA transactions

- 256K-Sample output data FIFO buffer; Configurable as open or closed (circular)

- Simultaneous output clocking, with emulated sequential outputs also supported

- Multiboard synchronization supported

- Continuous and Triggered-Burst output modes support seamless waveform sequencing

- Data clocking rate controlled internally or externally

- High accuracy ensured by on-demand Autocalibration of all channels

- x1 Link PCI Express Port operating at 2.5Gbps

- Available on multiple form factors, including PCI, cPCI and PC104-Plus, as well as PMC, PCIX and cPCIX. Contact Sales for availability

## **Applications Include:**

- ✓ Precision Voltage Array

- ✓ Servo Control

- ✓ Waveform Synthesis

- ✓ High Density Outputs

- ✓ Process Control

- ✓ Industrial Robotics

#### **PRELIMINARY**

REV: 101412

#### FUNCTIONAL DESCRIPTION

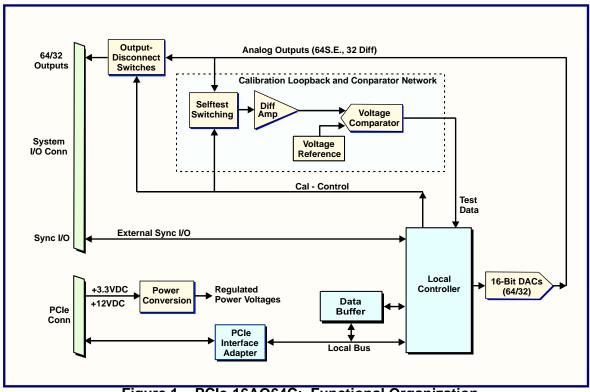

The PCIe-16AO64C is a precision 16-Bit analog output product that provides 64 simultaneously clocked output channels in a PCIe form factor. Outputs can be clocked at rates up to 500 KSPS per channel, and are supported by a 256K-Sample FIFO data buffer. Both continuous and burst clocking modes are supported, and voltage ranges are software-selectable as ±10V or ±5V; or optionally as 0 to +10V or 0 to +5V. Clocking and triggering rates can be derived from an internal rate generator, or from external clock and trigger sources to support the synchronous operation of multiple boards. When equipped with the optional outputs-disconnect feature, the outputs can be disconnected from the system I/O connector under software control.

Each analog output channel implements an R-2R DAC, which minimizes latency and has no minimum clocking rate. The outputs can be factory-configured for single-ended operation or for 3-wire balanced differential operation.

On-demand autocalibration determines and applies error correction for all output channels.

Figure 1. PCle-16AO64C; Functional Organization

Power requirements consist of +12VDC and +3.3VDC in compliance with the PCI Express specification, and analog power voltages are generated internally. Operation over the specified temperature range is achieved with conventional air cooling.

#### PERFORMANCE SPECIFICATIONS

At +25 °C, with specified operating voltages

### Analog Output Characteristics:

Configuration: 64 simultaneously clocked single-ended output channels with a dedicated 16-

Bit R-2R DAC per channel. Optionally available as 32-Channel 3-wire

balanced differential. 32SE/16Diff version also available

Voltage Ranges: Software-selectable as ±10V or ±5V. Optionally as 0 to +10V or 0 to +5V.

(Contact Sales for other, custom ranges)

Output Resistance: 1.0-Ohm maximum at I/O connector pins, without outputs-disconnect option;

or 2.5-Ohm maximum with outputs-disconnect. (Greater than 50 K-Ohms if

the outputs-disconnect feature is installed and enabled).

Output protection: Withstands sustained short-circuiting to ground

Loading: Zero to ±3ma, any single channel. Maximum total of 64mA on all outputs.

Stable with any load capacitance up to 20,000 PFD.

Line Imbalance: (With optional 3-Wire differential output configuration) ±10mV max.

Signal/Noise Ratio (SNR): 85dB typical on ±10V range; 10Hz - 250kHz. No filter.

Glitch Impulse: 10 nV-s, typical on the ±10V range

### Analog Output Transfer Characteristics:

| Resolution:    | 16 Bits (0.0015 percent of FSR) |

|----------------|---------------------------------|

| Output Access: | 256 K-Sample FIFO buffer.       |

| DC Accuracy: | S.E. Range | S.E. Zero Accuracy | S.E. ±Fullscale Accuracy |

|--------------|------------|--------------------|--------------------------|

|--------------|------------|--------------------|--------------------------|

(Max error, no-load) ±10V ±2.4mV ±3.3mV ±5V ±1.7mV ±2.5mV

±5V ±1.7mV ±2.5mV 0 to +10V ±2.2mV ±3.1mV 0 to +5V ±1.5mV ±2.3mV

<u>Diff Range\*</u> <u>Diff Zero Accuracy</u> <u>Diff +Fullscale Accuracy</u>

±10V ±2.4mV ±5.0mV ±5V ±1.7mV ±3.0mV 0 to +10V ±2.2mV ±4.5mV 0 to +5V ±1.5mV ±2.6mV

\* Differential output is measured between the even (HI) and odd (LO)

outputs in each even-odd channel pair.

Maximum Clocking Rate: 500KSPS.

Settling Time: 7us to 0.1 percent of step, typical with halfscale step and no output filter.

Bandwidth: 10kHz, 100kHz or No Filter (greater than 200kHz). See ordering options.

Crosstalk Rejection: 90 dB minimum, DC-100 kHz

Integral Nonlinearity: ±0.008 percent of FSR, maximum

Differential Nonlinearity: ±0.0035 percent of FSR, maximum (15 Bits DNL). Monotonic to 16 Bits.

Remote Ground Sense Input resistance approx 30KOhm when enabled, >1 Megohm when disabled.

Input range: ±2.0V; Protected to ±25V

Correction accuracy: ±1-percent. Bandwidth: DC-10kHz.

### **Analog Output Operating Modes and Controls**

Output Data Buffer: 256 K-sample FIFO

Sample Clock Sources: Internal rate generator; External Clock I/O, Software clock. 500kHz max.

Triggering Sources: Internal rate generator, TTL external trigger I/O, Software trigger.

Clocking Modes: Continuous or periodic. Supports triggered functions.

Internal Rate Generator: Programmable from 3 to 500,000 output clocks per second.

Divides Master Clock frequency to clocking rate using a 24-bit divider.

Output Filters: Single-pole lowpass filter, factory configured as: No filter, 100kHz, or 10kHz.

External Sync I/O: Bidirectional Clock and trigger, TTL

Output Data Format: 16 Bits, selectable as offset binary or two's complement coding, with attached

end-of-function flag and channel number.

Outputs Disconnect:

(Optional)

A single control bit disconnects all outputs from the system I/O connector.

### PCIe Compatibility:

Conforms to PCI Express Specification revision 1.0a. DMA transfers as bus master with two DMA channels.

### **Power Requirements:**

+3.3VDC ±0.2 VDC from the PCIe bus, 0.9 Amps typical, 1.0 Amps maximum.

+12VDC ±0.4 VDC from the PCle bus, 0.5 Amps typical, 0.6 Amps maximum.

Total power consumption: 9.4 Watts typical, 11 Watts maximum.

All outputs loaded with 1.0mA:

## Physical Dimensions::

Height: 110.1 mm (4.37 in)

Width: 18.7mm (0,74 in) not including bracket..21.6 mm (0.85 in) with Bracket.

Depth: 174.63 mm (6.60 in)

## **Environmental Specifications:**

Ambient Temperature Range:

Standard Temperature: Operating: 0 to +70 Degrees Celsius \*

Storage: -40 to +85 Degrees Celsius

Operating: -40 to +80 Degrees Celsius \*

Extended Temperature: Operating: -40 to +80 Degrees Celsius Storage: -40 to +85 Degrees Celsius

\* Air temperature at board surface.

Relative Humidity: 0 to 95%, non-condensing

Altitude: Operation to 10,000 ft.

Cooling: Conventional air cooling; 150 LFPM

## **Ordering Information:**

Specify the basic product model number followed by an option suffix "-A-B-C-D-E", as indicated below. For example, model number **PCle-16AO64C-64S-BP-F1-49.152M-OD-0** describes a module with 64 single-ended output channels, bipolar output ranges, no output filter, a 49.152MHz master clock frequency, Outputs-Disconnect feature installed, and no custom features

**Table 1. Ordering Options**

| Optional Parameter         | Value                                              | Specify Option As: |

|----------------------------|----------------------------------------------------|--------------------|

| Number of Channels:        | 64 Single-ended output channels                    | A = 64S            |

|                            | 32 Differential output channels                    | A = 32D            |

|                            | 32 Single-ended output channels                    | A = 32S            |

|                            | 16 Differential output channels                    | A = 16D            |

| Output Ranges:             | Bipolar: Software-selectable ±10V, ±5V.            | B = BP             |

|                            | Unipolar: Software-selectable 0 to +10V, 0 to +5V. | B = UP             |

| Output Filters 1           | No filter (~200kHz)                                | C= F1              |

|                            | 100kHz <sup>2</sup>                                | C= F2              |

|                            | 10kHz <sup>2</sup>                                 | C= F3              |

| Master Clock Frequency 1   | Standard 49.152MHz (25PPM)                         | D= 49.152M         |

|                            |                                                    |                    |

| Outputs Disconnect Feature | No Outputs Disconnect                              | E = 0              |

|                            | Outputs-Disconnect Feature Installed               | E = OD             |

| Custom Features:           |                                                    | F = 0              |

<sup>&</sup>lt;sup>1</sup> Contact factory for custom frequencies.

<sup>&</sup>lt;sup>2</sup> ±30% Typical.

Table 2. System I/O Connector

|     | Single-Ended Signal * |          |  |

|-----|-----------------------|----------|--|

| Pin | Row-A                 | Row-B    |  |

| 1   | OUT00                 | OUT34    |  |

| 2   | OUT01                 | OUT35    |  |

| 3   | OUT02                 | OUT36    |  |

| 4   | OUT03                 | OUT37    |  |

| 5   | OUT04                 | OUT38    |  |

| 6   | OUT05                 | OUT39    |  |

| 7   | OUT06                 | OUT40    |  |

| 8   | OUT07                 | OUT41    |  |

| 9   | OUT08                 | OUT42    |  |

| 10  | OUT09                 | OUT43    |  |

| 11  | OUT10                 | OUT44    |  |

| 12  | OUT11                 | OUT45    |  |

| 13  | OUT RTN               | OUT RTN  |  |

| 14  | OUT RTN               | OUT RTN  |  |

| 15  | OUT12                 | OUT46    |  |

| 16  | OUT13                 | OUT47    |  |

| 17  | OUT14                 | OUT48    |  |

| 18  | OUT15                 | OUT49    |  |

| 19  | OUT16                 | OUT50    |  |

| 20  | OUT17                 | OUT51    |  |

| 21  | OUT18                 | OUT52    |  |

| 22  | OUT19                 | OUT53    |  |

| 23  | OUT20                 | OUT54    |  |

| 24  | OUT21                 | OUT55    |  |

| 25  | OUT22                 | OUT56    |  |

| 26  | OUT23                 | OUT57    |  |

| 27  | OUT RTN               | OUT RTN  |  |

| 28  | OUT RTN               | OUT RTN  |  |

| 29  | OUT24                 | OUT58    |  |

| 30  | OUT25                 | OUT59    |  |

| 31  | OUT26                 | OUT60    |  |

| 32  | OUT27                 | OUT61    |  |

| 33  | OUT28                 | OUT62    |  |

| 34  | OUT29                 | OUT63    |  |

| 35  | OUT30                 | OUT RTN  |  |

| 36  | OUT31                 | OUT RTN  |  |

| 37  | OUT32                 | DIG RTN  |  |

| 38  | OUT33                 | CLK I/O  |  |

| 39  | OUT RTN               | DIG RTN  |  |

| 40  | REM GND               | TRIG I/O |  |

|     | O Connector           |          |  |

|-----|-----------------------|----------|--|

|     | Differential Signal * |          |  |

| Pin | Row-A                 | Row-B    |  |

| 1   | OUT00 HI              | OUT17 HI |  |

| 2   | OUT00 LO              | OUT17 LO |  |

| 3   | OUT01 HI              | OUT18 HI |  |

| 4   | OUT01 LO              | OUT18 LO |  |

| 5   | OUT02 HI              | OUT19 HI |  |

| 6   | OUT02 LO              | OUT19 LO |  |

| 7   | OUT03 HI              | OUT20 HI |  |

| 8   | OUT03 LO              | OUT20 LO |  |

| 9   | OUT04 HI              | OUT21 HI |  |

| 10  | OUT04 LO              | OUT21 LO |  |

| 11  | OUT05 HI              | OUT22 HI |  |

| 12  | OUT05 LO              | OUT22 LO |  |

| 13  | OUT RTN               | OUT RTN  |  |

| 14  | OUT RTN               | OUT RTN  |  |

| 15  | OUT06 HI              | OUT23 HI |  |

| 16  | OUT06 LO              | OUT23 LO |  |

| 17  | OUT07 HI              | OUT24 HI |  |

| 18  | OUT07 LO              | OUT24 LO |  |

| 19  | OUT08 HI              | OUT25 HI |  |

| 20  | OUT08 LO              | OUT25 LO |  |

| 21  | OUT09 HI              | OUT26 HI |  |

| 22  | OUT09 LO              | OUT26 LO |  |

| 23  | OUT10 HI              | OUT27 HI |  |

| 24  | OUT10 LO              | OUT27 LO |  |

| 25  | OUT11 HI              | OUT28 HI |  |

| 26  | OUT11 LO              | OUT28 LO |  |

| 27  | OUT RTN               | OUT RTN  |  |

| 28  | OUT RTN               | OUT RTN  |  |

| 29  | OUT12 HI              | OUT29 HI |  |

| 30  | OUT12 LO              | OUT29 LO |  |

| 31  | OUT13 HI              | OUT30 HI |  |

| 32  | OUT13 LO              | OUT30 LO |  |

| 33  | OUT14 HI              | OUT31 HI |  |

| 34  | OUT14 LO              | OUT31 LO |  |

| 35  | OUT15 HI              | OUT RTN  |  |

| 36  | OUT15 LO              | OUT RTN  |  |

| 37  | OUT16 HI              | DIG RTN  |  |

| 38  | OUT16 LO              | CLK I/O  |  |

| 39  | OUT RTN               | DIG RTN  |  |

| 40  | REM GND               | TRIG I/O |  |

Figure 2. System I/O Connector

#### **System Mating Connector:**

Standard 80-pin 0.050" dual-ribbon socket connector:

Robinson Nugent **P50E-080S-TG** or equivalent.

General Standards Corporation assumes no responsibility for the use of any circuits in this product. No circuit patent licenses are implied. Information included herein supersedes previously published specifications on this product and is subject to change without notice.

Row B

Connector

Pin 40

Panel

Bracket

Pin 1

Circuit

Board

Pin View

<sup>\*</sup> Outputs can be factory-configured for either single-ended or differential operation.