# General Standards Corporation

**High Performance Bus Interface Solutions**

# 66-18AI64SSC750K

# 64-Channel, 18-Bit Simultaneous Sampling **Analog Input Board**

With 750 KSPS Sample Rate per Channel and 66 MHz PCI Support

Available also in PMC, PCI, cPCI and PC104-Plus and PCI Express form factors as:

| PMC66-18AI64SSC750K:     | PMC, Single-width                    |

|--------------------------|--------------------------------------|

| PCI66-18AI64SSC750K:     | PCI, short length                    |

| Cpci66-18AI64SSC750K:    | <b>cPCI</b> , 3U                     |

| PC104P66-18AI64SSC750K:  | PC104-Plus                           |

| PCIe66-18AI64SSC750K:    | PCI Express                          |

| PCIe10466-18AI64SSC750K: | PCIe, one-lane on PC/104 form factor |

|                          |                                      |

See Ordering Information for details. Call for availability of other form factors, such as XMC, CCPMC, etc.

# Features

- 64 Analog inputs with dedicated 18-Bit SAR ADC per Channel

- Simultaneous sampling of all inputs; Minimum Data Skew

- Sampling Rates to 750 KSPS per channel (48 MSPS aggregate rate)

- **Continuous, Burst and Single-Sample Clocking Modes**

- Software and I/O pinout compatibility with the 16AI64SSA/C

- Selectable Differential Processing Simulates Differential Operation of Channel Pairs

- Input Ranges software-selectable as  $\pm 10V$ ,  $\pm 5V$ , and 0 to  $\pm 10V$ , or optionally as ±5V, ±2.5V, 0 to +10V, and 0 to +5V

- Hardware Sync I/O for Multiboard Operation

- FIFO buffer provides 256 K-Sample data capacity at 18 bits; 512K at 16 bits with data packing.

- A software-selectable low-latency configuration provides 64 registers that duplicate the last sample from all A/D converters

- 2-Channel DMA Engine

- Sampling and burst triggering controlled by internal rate generators, or by direct software control, or externally

- On-demand internal autocalibration of all channels

- Completely software-configurable; No field jumpers

- D32; 66MHz, 33MHz PCI compatibility, with universal 5V/3.3V Signaling

- Internal Sync/Clock I/O connector provides behind-panel access to clock and sync signals

- PMC version protected with integral EMI shield over analog components

# Typical Applications

- ✓ High-Density Analog Inputs

- ✓ Industrial Robotics

- ✓ Acoustic Sensor Arrays

- ✓ Analog Event Capture

- ✓ Biometric Signal Analysis

- ✓ Dynamic Test Systems

- PRELIMINARY -

Rev: 021214

# **Functional Description**

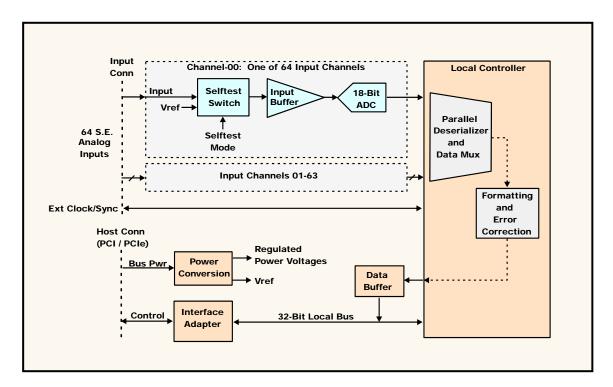

The 18-Bit 66-18Al64SSC750K analog input board samples and digitizes 64 input channels simultaneously at rates up to 750,000 samples per second for each channel. Each input channel contains a dedicated 18-Bit sampling ADC, and the resulting 18-bit sampled data is available to the PCI bus through a 256 K-Sample FIFO buffer. Throughput capacity is further enhanced with 66MHz PCI support and increased local clocking frequency. All operational parameters are software configurable.

Inputs can be sampled in groups of 1, 2, 4, 8, 16, 32 or 64 channels; or software can select a first and last channel to be acquired. The sample clock can be generated from an internal rate generator, or by software or external hardware. Input ranges are software-selectable as  $\pm 10V$ ,  $\pm 5V$ , and 0 to  $\pm 10V$ , or optionally as  $\pm 5V$ ,  $\pm 2.5V$ , 0 to  $\pm 10V$ , and 0 to  $\pm 5V$ .

An on-demand autocalibration feature determines offset and gain correction values for each input channel, and applies the corrections digitally during acquisition. A selftest switching network routes calibration reference signals to each channel through internal selftest switches, and permits board integrity to be verified by the host.

Figure 1. PM66-18AI64SSC750K; Functional Organization

This product is functionally compatible with the IEEE PCI local bus specification Revision 2.3 for PMC, PC104 *Plus*, or PCI products, or with the PCIe Specification revision 2.0 for PCI Express products. System input/output connections are made at the front panel through a single high-density connector. Operation over the specified temperature range is achieved with conventional convection cooling.

# **Performance Specifications**

$\overline{\text{At} + 25 ^{\text{O}}\text{C}}$ , with specified operating conditions, and with differential processing deselected

## Input Characteristics:

|   | -                                                                  |                                                                                                                                                                                                                                                                                                        |  |  |

|---|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | Configuration:                                                     | 64 single-ended analog input channels; Dedicated 18-Bit SAR ADC per channel.<br>Optional 32-Channel version available.                                                                                                                                                                                 |  |  |

|   | Voltage Ranges:                                                    | Software configurable as $\pm 10V$ , $\pm 5V$ , 0 to $\pm 10V$ .<br>(Optionally $\pm 5V$ , $\pm 2.5V$ , 0 to $\pm 10V$ , 0 to $\pm 5V$                                                                                                                                                                 |  |  |

|   | Input Impedance:                                                   | All input ranges: 350 KOhms minimum.                                                                                                                                                                                                                                                                   |  |  |

|   | Bias Current:                                                      | (Inputs grounded; typical values):<br>High Ranges: 8ua, 4ua, 0.3ua on ±10V, ±5V, 0 to +10V ranges, respectively.                                                                                                                                                                                       |  |  |

|   |                                                                    | Low Ranges: 12ua, 7ua, 0.9ua, 0.5ua on ±5V, ±2.5V, 0 to +10V, 0 to +5V ranges.                                                                                                                                                                                                                         |  |  |

|   | Crosstalk Rejection:                                               | 90dB typical, DC-50kHz                                                                                                                                                                                                                                                                                 |  |  |

|   | Input Noise:                                                       | <ul> <li>High range set (±10V) typical:</li> <li>0.2 mVRMS; typical for bipolar ranges; 0.35mVRMS for unipolar ranges.</li> <li>0.01-350kHz (91dB SNR on ±10V range).</li> <li>Low range set (±5V) typical:</li> <li>0.15 mVRMS; typical for bipolar ranges; 0.25mVRMS for unipolar ranges.</li> </ul> |  |  |

|   |                                                                    | (Noise increases approximately 45-percent with differential processing selected).                                                                                                                                                                                                                      |  |  |

|   | Fault Protection:                                                  | Sustains $\pm 40$ Volts with power removed; $\pm 25V$ with power applied.                                                                                                                                                                                                                              |  |  |

| T | ransfer Characteristics:                                           |                                                                                                                                                                                                                                                                                                        |  |  |

|   | Resolution:                                                        | 18 Bits (0.0004 percent of FSR)                                                                                                                                                                                                                                                                        |  |  |

|   | Maximum Sample Rate:                                               | 750 KSPS per channel                                                                                                                                                                                                                                                                                   |  |  |

|   | Channels per Sample:                                               | 1, 2, 4, 8, 16, 32 or 64 channels, or first and last channel selection.                                                                                                                                                                                                                                |  |  |

|   | DC Accuracy:<br>(Maximum composite error after<br>autocalibration) | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                 |  |  |

|   | Input Bandwidth (-3dB):                                            | DC to 340 kHz typical. See ordering options for custom bandwidths.                                                                                                                                                                                                                                     |  |  |

|   | Integral Nonlinearity:                                             | ±0.002 percent of FSR, maximum                                                                                                                                                                                                                                                                         |  |  |

|   | Differential Nonlinearity:                                         | ±0.001 percent of FSR, maximum                                                                                                                                                                                                                                                                         |  |  |

|   | ··································                                 | the first state and management                                                                                                                                                                                                                                                                         |  |  |

## Analog Input Operating Modes and Controls:

| Input Data Buffers:      | FIFO: 256 K-Samples in 18-Bit mode; 512 K-Samples in 16-Bit packed-data mode. An alternative 'Low-Latency' array of 64 data registers is available in addition to the FIFO.                                                                        |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sample Clock Sources:    | Internal rate generator; External Hardware Trigger I/O, Software clock.<br>Continuous, Burst and Single-Sample Clocking Modes.                                                                                                                     |  |

| Rate Generators:         | Two 24-Bit Generators, Rate-A and Rate-B; both divide the master clock frequency to the required clock and trigger rates.                                                                                                                          |  |

| External TTL Sync:       | Bidirectional TTL Sample Clock and Burst Trigger lines. These signals are duplicated internally through an internal Sync-I/O connector.                                                                                                            |  |

| Internal Clock/Sync I/O: | Internal Sync-I/O connector provides internal (behind-panel) access to clock and sync signals.                                                                                                                                                     |  |

| Input Data Format:       | Nonpacked Mode: 18-Bit data word plus single-bit Channel-00 tag.<br>Packed Mode: Lword sync code followed by packed 16-BIt channel data.<br>Even-numbered channels occupy the lower word (D00-15);<br>odd channels occupy the upper word (D16-31). |  |

| Data Format:             | Selectable as offset binary or two's complement.                                                                                                                                                                                                   |  |

| Triggered Bursts:        | Data can be acquired in triggered bursts, with up to 1,048,575 samples per burst, or in bursts of indefinite length.                                                                                                                               |  |

| Differential Processing: | A selectable processing option processes input data as 63 pseudo-differential channels (common return) or as 32 full-differential channels.                                                                                                        |  |

## Host Control Interface Compatibility:

#### PCI, PMC, cPCI and PC104 Plus:

Conforms to PCI Specification 2.3, with D32 read/write transactions and universal 5V/3.3V signaling..

Supports block-mode DMA transfers as bus master. Provides a multifunction interrupt.

#### **PCI Express:**

PCIe Specification revision 2.0; single-lane. Supports block-mode and demand-mode DMA transfers as bus master.

## **Physical Parameters**

## **Power Requirements:**

PCI, PMC, cPCI and PC104 Plus form factors: +5.0 VDC ±0.25 VDC at: 1.1 Amps typical, 1.4 Amps, maximum

#### **PCI Express Form Factor**

+3.3±0.3VDC at 1.0 Amps typ; 1.2 Amps max. +12.0±0.8VDC at 0.2 Amp typ; 0.3 Amp max.

### **Physical Dimensions:**

#### **PMC Form Factor**

Height: 13.5 mm (0.53 in), Width: 74.0 mm (2.91 in) Depth: 143.75 mm (5.66 in)

#### **PCI Express Form Factor**

| Height: | 12.4 mm (0.49 in)  |

|---------|--------------------|

| Width:  | 110.1 mm (4.37 in) |

| Depth:  | 167.6 mm (6.60 in) |

## **Environmental Specifications:**

Ambient Temperature Range:

| Standard Temperature: | Operating: 0 to +70 Degrees Celsius *<br>Storage: -40 to +85 Degrees Celsius   |  |  |

|-----------------------|--------------------------------------------------------------------------------|--|--|

| Extended Temperature: | Operating: -40 to +80 Degrees Celsius *<br>Storage: -40 to +85 Degrees Celsius |  |  |

|                       | * Air temperature at board surface.                                            |  |  |

| Relative Humidity:    | 0 to 95%, non-condensing                                                       |  |  |

| Altitude:             | Operation to 10,000 ft.                                                        |  |  |

| Cooling:              | Conventional air cooling; 150 LFPM                                             |  |  |

Specify the basic product model number followed by an option suffix "-A-B-C-D-E", as indicated below. For example, model number PMC66-18AI64SSC750K-64-60.00M-340K-RTN-5V describes a board with 64 input channels, a standard 60MHz master clock frequency, standard 340kHz bandwidth, Standard INP RTN pin, ±5V maximum input range, and no custom features.

| Basic Model Number                     | Form Factor                          |

|----------------------------------------|--------------------------------------|

| PMC66-18AI64SSC750K                    | PMC (Native)                         |

| PCI66-18AI64SSC750K <sup>1</sup>       | PCI, short length                    |

| Cpci66-18Al64SSC750K <sup>1</sup>      | cPCI, 3U                             |

| PCIe66-18AI64SSC750K <sup>1</sup>      | cPCI, 3U                             |

| PC104P66-18AI64SSC750K                 | PC104-Plus                           |

| PCIe10466-18AI64SSC750K <sup>1,2</sup> | PCIe, one-lane on PC/104 form factor |

<sup>1</sup> Module installed and tested on an adapter, with mechanical and functional equivalency. Contact factory for availability in native form factors.

<sup>2</sup> PCIe104 supports only the PCIe bus.

| Optional Parameter                                                | Value                                          | Specify Option As:    |

|-------------------------------------------------------------------|------------------------------------------------|-----------------------|

| Number of Input Channels                                          | 64 Channels                                    | A = 64                |

|                                                                   | 32 Channels                                    | A = 32                |

| Master Clock Frequency <sup>1</sup> 60.00 MHz                     |                                                | B = 60M               |

|                                                                   |                                                | B = (XX.XXX MHz)M     |

| Custom Input Bandwidth, -3dB <sup>2</sup>                         | Standard 340kHz                                | C =340K               |

|                                                                   | 70kHz                                          | C = 70K               |

|                                                                   |                                                | C = (Freq, kHz)K      |

| INPUT RTN / CLK I/O                                               | Configured as an INPUT RTN pin                 | D = RTN               |

| Pin B33 configuration Configured as an active CLK I/O pin. D = CL |                                                | D = CLK               |

| Input Ranges                                                      | Selectable as: ±10V, ±5V, 0 to +10V            | E = 10V or 0 (Zero)   |

|                                                                   | Selectable as: ±5V, ±2.5V, 0 to +10V, 0 to +5V | E = 5V                |

| Custom Feature                                                    | No custom features                             | F = 0 (Zero) or blank |

<sup>1</sup> Custom clock frequencies available from 58-62MHz. Call for availability.

$^2$  Custom bandwidths available from 10kHz to 1.0MHz. ±20%. Call for availability.

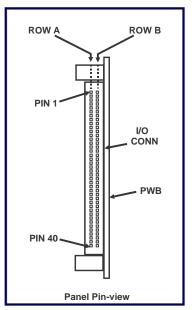

| Table 1. System I/O Connecto | Table 1. | System | I/O C | onnecto |

|------------------------------|----------|--------|-------|---------|

|------------------------------|----------|--------|-------|---------|

| _ |       | -         | - |       |                                  |  |

|---|-------|-----------|---|-------|----------------------------------|--|

|   | ROW-A |           |   | ROW-B |                                  |  |

|   | PIN   | SIGNAL    |   | PIN   | SIGNAL                           |  |

|   | 1     | INP00     |   | 1     | INP32                            |  |

|   | 2     | INP01     |   | 2     | INP33                            |  |

|   | 3     | INP02     |   | 3     | INP34                            |  |

| ľ | 4     | INP03     |   | 4     | INP35                            |  |

| Ĩ | 5     | INPUT RTN |   | 5     | INPUT RTN                        |  |

| Ĩ | 6     | INP04     |   | 6     | INP36                            |  |

| ĺ | 7     | INP05     |   | 7     | INP37                            |  |

| ľ | 8     | INP06     |   | 8     | INP38                            |  |

|   | 9     | INP07     |   | 9     | INP39                            |  |

|   | 10    | INPUT RTN |   | 10    | INPUT RTN                        |  |

| Ĩ | 11    | INP08     |   | 11    | INP40                            |  |

| Ĩ | 12    | INP09     |   | 12    | INP41                            |  |

|   | 13    | INP10     |   | 13    | INP42                            |  |

|   | 14    | INP11     |   | 14    | INP43                            |  |

|   | 15    | INPUT RTN |   | 15    | INPUT RTN                        |  |

|   | 16    | INP12     |   | 16    | INP44                            |  |

| Ĩ | 17    | INP13     |   | 17    | INP45                            |  |

| ľ | 18    | INP14     |   | 18    | INP46                            |  |

|   | 19    | INP15     |   | 19    | INP47                            |  |

|   | 20    | INPUT RTN |   | 20    | INP48                            |  |

|   | 21    | INP16     |   | 21    | INPUT RTN                        |  |

|   | 22    | INP17     |   | 22    | INP49                            |  |

|   | 23    | INP18     |   | 23    | INP50                            |  |

|   | 24    | INP19     |   | 24    | INP51                            |  |

|   | 25    | INPUT RTN |   | 25    | INP52                            |  |

|   | 26    | INP20     |   | 26    | INP53                            |  |

|   | 27    | INP21     |   | 27    | INPUT RTN                        |  |

|   | 28    | INP22     |   | 28    | INP54                            |  |

|   | 29    | INP23     |   | 29    | INP55                            |  |

|   | 30    | INPUT RTN |   | 30    | INP56                            |  |

|   | 31    | INP24     |   | 31    | INP57                            |  |

|   | 32    | INP25     |   | 32    | INP58                            |  |

|   | 33    | INP26     |   | 33    | INPUT RTN / CLK I/O <sup>1</sup> |  |

| ĺ | 34    | INP27     |   | 34    | INP59                            |  |

|   | 35    | INPUT RTN |   | 35    | INP60                            |  |

|   | 36    | INP28     |   | 36    | INP61                            |  |

|   | 37    | INP29     |   | 37    | INP62                            |  |

|   | 38    | INP30     |   | 38    | INP63 / CLK I/O <sup>2</sup>     |  |

|   | 39    | INP31     |   | 39    | TRIG I/O RTN                     |  |

|   | 40    | INPUT RTN |   | 40    | TRIG I/O                         |  |

<sup>1</sup> This pin can be factory configured either as an INPUT RTN. pin or as a CLK I/O pin. See ordering options. (Note: Configuring this pin as a CLK I/O pin prevents 100% pin-compatibility with the 16Al64SSC board).

<sup>2</sup> Software-programmable as either analog Input Channel 63, as a CTL bidiractional CLK I/O pin

or as a TTL bidirectional CLK I/O pin.

Figure 2. System Input Connector

**System Mating Connector:**

Standard 80-pin 0.050" dual-ribbon socket connector: 3M# P50E-080S-EA, or equivalent.

| SYNC-I/O CONN PIN <sup>1</sup> | SIGNAL                                                |

|--------------------------------|-------------------------------------------------------|

| 1                              | DIG RTN                                               |

| 2                              | AUX CLOCK                                             |

| 3                              | DIG RTN                                               |

| 4                              | AUX TRIGGER                                           |

| 5                              | DIG RTN                                               |

| 6                              | Reserved. Connect to INPUT RTN or leave disconnected. |

#### Table 2. Internal Sync-I/O Connector

General Standards Corporation assumes no responsibility for the use of any circuits in this product. No circuit patent licenses are implied. Information included herein supersedes previously published specifications on this product and is subject to change without notice.

## **General Standards Corporation**

8302A Whitesburg Drive · Huntsville, AL 35802 Phone: (256) 880-8787 or (800) 653-9970 FAX: (256) 880-8788 Email: Solutions@GeneralStandards.com