# XPedite2470

# 3U VPX Virtex-7 FPGA Module with FMC Site and Freescale P1010 Processor

- > Xilinx Virtex-7 FPGA XC7VX485T

- > 3U VPX (VITA 46) module

- FMC-compliant carrier card (VITA 57) with High Pin Count (HPC) connector

- Freescale QorlQ P1010 processor with one Power Architecture® e500 core at up to 800 MHz

- Up to 512 MB of DDR3L-800 ECC SDRAM for P1010

- Up to 16 GB of SPI flash (with redundancy) for P1010

- Up to 1 GB of NAND flash for P1010

- Four channels of x32 DDR3L SDRAM, up to 1 GB each for FPGA

- 128 MB of user NOR flash for FPGA

- LVDS and high-speed GTX transceiver connectivity between FPGA and FMC

- One MicroSD socket

- x1 PCI Express P1010 to FPGA interconnect

- Two SerDes Gigabit Ethernet P1 fabric interconnects (P1010)

- Optional 10/100/1000BASE-T Ethernet port (P1010)

- Eight high-speed GTX lanes to FMC

- Eleven high-speed GTX lanes to P1 fabric interconnect

- Up to two RS-232/422/485 serial P2 ports (P1010)

- One USB 2.0 port (P1010)

- FPGA Development Kit (FDK)

- Linux BSP

# XPedite2470

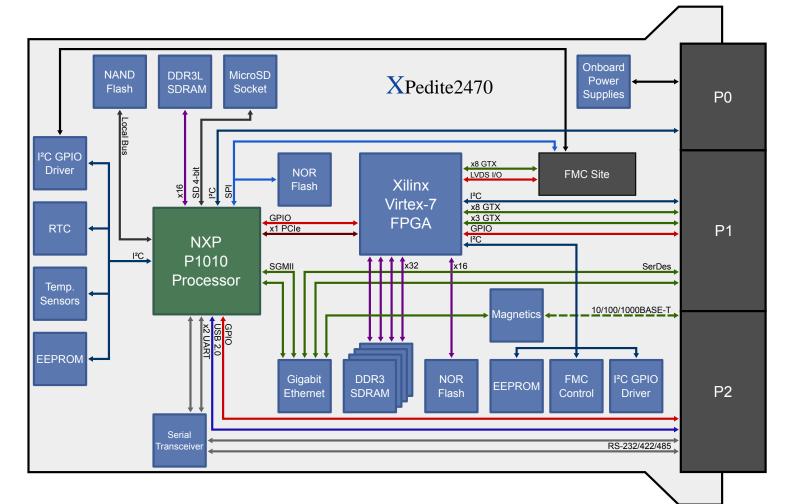

The XPedite2470 is a high-performance, reconfigurable, conduction- or air-cooled, 3U VPX, FPGA processing module based on the Xilinx Virtex-7 family of FPGAs. With multiple high-speed fabric interfaces, external memory, Virtex-7 FPGA, an FMC site, and high-density I/O, the XPedite2470 is ideal for customizable, high-bandwidth, signal-processing applications.

The XPedite2470's DDR3L SDRAM and flexible I/O routing makes it perfect for high-speed, bandwidth-intensive, data-streaming applications. The card provides numerous I/O capabilities through its FMC daughter card interface, allowing access to single-ended and differential I/O and configurable GTX transceivers. An FMC daughter card can expand the capabilities of the XPedite2470 by providing technologies such as Digital Signal Processing (DSP), high-frequency Digital-to-Analog Conversion (DAC), and high-frequency Analog-to-Digital Conversion (ADC).

The XPedite2470 supports a high-performance Freescale P1010 QorlQ processor. With a Power Architecture® e500 core running at up to 800 MHz, the P1010 provides hybrid signal processing with the combination of an FPGA and a general-purpose processor on one 3U VPX module. With the flexibility of the FMC interface, high-speed streaming data can be brought directly into the FPGA and processed, then transferred over a high-speed PCIe interface to the P1010 processor for further processing and analysis.

The XPedite2470 provides a high-performance, feature-rich solution capable of interfacing to and processing streaming data from a wide variety of sensors. The X-ES FPGA Development Kit (FDK) is provided to support the requirements of high-performance, real-time, embedded streaming data applications and simplify FPGA development. It includes IP blocks, example FPGA designs, and software to control and communicate with FPGAs. A Linux Board Support Package (BSP) is available.

...Always Fast

## **Extreme Engineering Solutions**

3225 Deming Way, Suite 120 • Middleton, WI 53562 Phone: 608.833.1155 • Fax: 608.827.6171 sales@xes-inc.com • http://www.xes-inc.com

www.xes-inc.com

## **FPGA**

- Xilinx Virtex-7 for high-performance logic and DSP applications

- · Up to 4 GB of DDR3L SDRAM in four channels

- 128 MB of user NOR flash

## **Supported FPGAs**

- Xilinx Virtex-7 XC7VX330T

- Xilinx Virtex-7 XC7VX415T

- Xilinx Virtex-7 XC7VX485T (default)

- Xilinx Virtex-7 XC7VX690T

- Support for commercial and industrial temperature as well as -1, -2, -3 speed grades

## FMC (VITA 57)

- FPGA LVDS I/O

- x8 GTX transceivers

- FPGA and processor GPIO via I2C expanders

- VPX GPIO

- RS-232/485 serial ports

- SPI and I<sup>2</sup>C interfaces

- Support for 1.8 V, 1.5 V, 1.2 V, and 1.35 V VADJ

#### **Processor**

- · Freescale QorlQ P1010 processor

- Power Architecture® e500 core at up to 800 MHz

- 256 kB L2 cache

- Up to 512 MB of DDR3L-800 ECC SDRAM

- Up to 16 MB of NOR flash (with redundancy)

- . Up to 1 GB of NAND flash

## **VPX (VITA 46) P1 I/O**

- Up to x8 PCI Express P1.A

- Three additional GTX lanes

- Two SerDes Gigabit Ethernet ports (or one SerDes port out P1 and one 10/100/1000BASE-T port out P2)

## **VPX (VITA 46) P2 I/O**

- One 10/100/1000BASE-T port (when two SerDes Gigabit Ethernet P1 ports are not used)

- Up to two RS-232/422/485 serial ports

- One USB 2.0 port

- 3.3 V GPIO signals

- FGPA LVDS GPIO

- P1010 GPIO

- FMC GPIO

# **Development Support**

- X-ES FPGA Development Kit (FDK)

- Linux BSP

## **Physical Characteristics**

- 3U VPX-REDI conduction- or air-cooled form factor

- Dimensions: 100 mm x 160 mm

- 0.8 in. pitch without solder-side cover

- 0.85 in. and 1.0 in. pitch with solder-side cover

## **Environmental Requirements**

Contact factory for appropriate board configuration based on environmental requirements.

- Supported ruggedization levels (see chart below): 1, 3, 5

- Conformal coating available as an ordering option

# **Power Requirements**

Power will vary based on configuration and usage.

Please consult factory.

| Ruggedization Level   | Level 1                             | Level 3                            | Level 5                                        |

|-----------------------|-------------------------------------|------------------------------------|------------------------------------------------|

| Cooling Method        | Standard Air-Cooled                 | Rugged Air-Cooled                  | Conduction-Cooled                              |

| Operating Temperature | 0 to +55°C ambient (300 LFM)        | -40 to +70°C (600 LFM)             | -40 to +85°C (board rail surface)              |

| Storage Temperature   | -40 to +85°C ambient                | -55 to +105°C ambient              | -55 to +105°C (maximum)                        |

| Vibration             | 0.002 g²/Hz (maximum), 5 to 2000 Hz | 0.04 g²/Hz (maximum), 5 to 2000 Hz | 0.1 g <sup>2</sup> /Hz (maximum), 5 to 2000 Hz |

| Shock                 | 20 g, 11 ms sawtooth                | 30 g, 11 ms sawtooth               | 40 g, 11 ms sawtooth                           |

| Humidity              | 0% to 95% non-condensing            | 0% to 95% non-condensing           | 0% to 95% non-condensing                       |