当社で取り扱っている各種ボード製品に関連する技術情報ライブラリです。

当社で取り扱っている各種ボード製品に関連する技術情報ライブラリです。

カテゴリを選択すると関連する技術情報が表示されます。製品ページで不明な用語や規格の概要などをご確認いただけます。また、テックジャーナル(年1回発行)も併せてご確認ください。▶ テックジャーナル

FPGA

FPGAモデルの違いや開発方法を解説

FPGAとは

-

▮ Field Programmable Gate Array の略で、フィールドで再構成可能(プログラマブル)な論理回路デバイス

▮ ASICやASSP(専用LSI)と比較して、ユーザがプログラム可能なため柔軟性に優れている

▮ 製造メーカーは、AMD(旧Xilinx), Intel(旧Altera)が2大FPGAサプライヤでありその他LatticeやMicrochipなども小規模のFPGAをリリースしている

▮ 開発言語はハードウェア記述言語(HDL)を使用して行うが、近年はC言語や機能ブロック(モデルベースデザイン)などの開発手法も実用的になっている

▮ 弊社で取り扱っている製品はほとんどがXilinxのデバイスを使用している

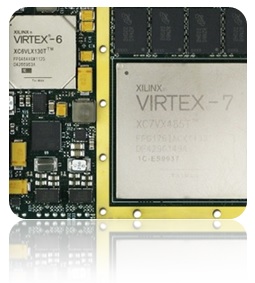

Virtex-7

-

▮ 2010年にXilinx社がリリースした「7シリーズ」のハイエンドモデルFPGA

▮ Virtex-6の2倍のシステム性能と容量を実現するよう最適化された高性能のFPGA

▮ SSI (スタックドシリコンインターコネクト)テクノロジによって高集積化を実現

▮ 最大200万ロジックセル、VCXOコンポーネント、AXI IP、AMSを統合

▮ 最大2.8Tb/sのシリアル総帯域幅、最大96個の13.1G GT、最大16個の28.05G GT

▮ 5,335GMAC、68Mb BRAM、DDR3-1866対応

Kintex-7

-

▮ 2010年にXilinx社がリリースした「7シリーズ」のミドルクラスFPGA

▮ Virtex-6の2倍の対価格性能を実現するよう最適化された新しいクラスのFPGA

▮ Virtex-6と同等性能でありながら、コスト・消費電力50%削減を実現

▮ 最大478,000ロジックセル、VCXOコンポーネント、AXI IP、AMSを統合

▮ 最大32個の12.5G GT

▮ 2,845GMACS、34Mb BRAM、DDR3-1866対応

Virtex-6

-

▮ 2009年にXilinx社がリリースした40nmプロセスのFPGAデバイス

▮ Virtex-5と比較して最大50%の消費電力低減と20%のコストダウンを実現

▮ ロジック用に最適化されたLXT、信号処理用に最適化されたSXT、高速シリアル通信に最適化されたHXTがある

▮ 最大6.6Gbpsで動作可能なGTXトランシーバ

▮ PCI Express Gen2に対応したインターフェイスブロックを内蔵

▮ 10/100/1000 Mb/sイーサネットMACブロックを内蔵

Virtex-5

-

▮ 2006年にXilinx社がリリースした65nmプロセスのFPGAデバイス

▮ Virtex-4 と同様、ロジック/信号処理/プロセッサ/高速シリアルの各アプリケーションごとに特化したアーキテクチャをとりつつ、より高いパフォーマンスと低消費電力を目指して開発されたFPGA

▮ ロジック用のLX、超高性能ロジック用のLXT、信号処理/ シリアル通信用のSXT、高速シリアル通信を備えたFXT シリーズがある

▮ より柔軟性の増したロジック、DSP 機能

▮ PCI Express エンドポイント内蔵

▮ ギガビットイーサネット MAC 内蔵

Virtex-4

-

▮ 2004年にXilinx社がリリースした90nmプロセスのマルチプラットフォームFPGAデバイス

▮ ロジック用に最適化されたLX、信号処理用に最適化されたSX、高速シリアル通信に最適化されたFX シリーズがある

▮ Virtex-4 はロジック/信号処理/プロセッサ/高速シリアルの各アプリケーションごとに特化したアーキテクチャをとることで、それぞれの分野で最高のパフォーマンスと最小の消費電力を達成することを目的として開発

▮ 高度なクロック管理と柔軟なメモリ構成

▮ 最高で 6.5Gbps のシリアルトランシーバ

▮ DSP 機能

Kintex-UltraScale

-

▮ 2014年にXilinx社がリリースした「UltraScaleシリーズ」のエントリークラスFPGA

▮ 対コスト性能に優れたXilinx UltraScaleアーキテクチャFPGA

▮ Kintex-7と比べて単位ワットあたり 2倍以上のシステムレベル性能

▮ モノリシックデバイスと次世代スタックドシリコンインターコネクト (SSI) テクノロジを採用したデバイスの両方で展開

▮ DSPおよびブロックRAMの対ロジック比率が高い

▮ 次世代トランシーバーを搭載

Virtex-UltraScale

-

▮ 2014年にXilinx社がリリースした「UltraScaleシリーズ」のハイエンドクラスFPGA

▮ 容量および性能共に優れた Xilinx UltraScaleアーキテクチャFPGA

▮ モノリシックデバイスと次世代の SSI テクノロジデバイスの両方で展開

▮ 最高のシステム容量、 帯域幅、 性能を提供

▮ 20nmプロセスルールを採用

Zynq-7000

-

▮ 2013年にXilinx社がリリースした、ARMプロセッサを統合したシステムオンチップFPGAデバイス

▮ Arm Cortex™-A9 プロセッサと 28nm Artix®-7 ベースのプログラマブル ロジックを統合

▮ 単位ワットあたり優れた性能および最大の設計柔軟性を提供

▮ 6.25Gb/s トランシーバーと一般的なハード ペリフェラルを搭載

▮ XilinxのFPGAで最も低価格なシリーズ

Zynq UltraScale+

-

▮ 2019年にXilinx社がリリースした「UltraScale+シリーズ」の最高性能SoC FPGAデバイス

▮ プロセッシングに特化したMPSoC、RF-AD/DAに特化したRFSoCがある

▮ TSMC 社の 16FinFET+ プロセス テクノロジを採用

▮ 64 ビットのクワッド コア Arm Cortex-A53 プロセッサ搭載

▮ 次世代 AXI インターコネクト採用

▮ RF データコンバーターと SD-FEC (Soft-Decision Forward Error Correction) を単一の SoC アーキテクチャに統合

Stratix 10 AX

-

▮ Intel社がリリースした「Stratix 10シリーズ」の最高性能SoC FPGAデバイス

▮ 最大64DSPS超広帯域のAD/DAを内蔵し、ダイレクトRFサンプリングを実現

▮ Intel社の 14nm プロセス テクノロジを採用

▮ 最大1.5GHzのクアッド コア Arm Cortex-A53 MP-Coreプロセッサ搭載

▮ インテル Hyperflex™ FPGA アーキテクチャ採用

Versal ACAP

-

▮ Xilinx社(AMD社)がリリースしたディープラーニングやAIの処理に特化したFPGAデバイス

▮ スカラープロセッサ, プログラマブルロジック, AI アクセラレータの3種類のエンジンを搭載

▮ TSMC社の7nm FinFETプロセステクノロジを使用

▮ クラウド、無線通信、エッジコンピューティング、自動運転、航空宇宙、防衛など用途別にシリーズ化

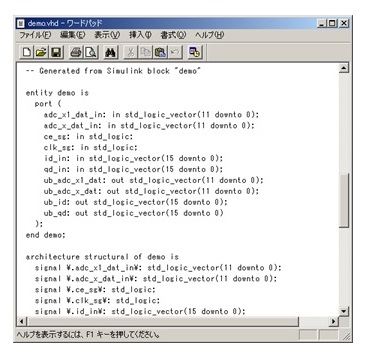

FPGA開発手法(VHDL/Verilog)

-

▮ VHDL/Verilog ハードウェア記述言語を使用してFPGA コードをダイレクトに記述する方法

▮ FPGA 開発用のFPGA デザインキットが用意されており、リファレンスデザインにはユーザアルゴリズムを実装しやすいようにユーザブロックが予め準備されている

▮ ユーザはユーザブロックのエリアのみ開発する事でFPGA にアルゴリズムを実装する事が可能

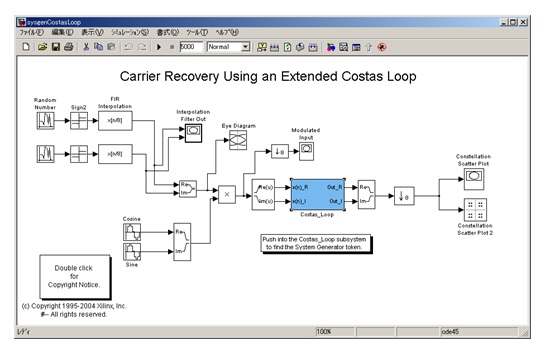

FPGA開発手法(MATLAB/SimuLink)

-

▮ Mathworks社のMATLAB/SimuLink とXilinx社のSystem Generatorを使用したモデルベースのFPGA開発手法

▮ VHDL/Verilog 等のハードウェア記述言語を理解されていないユーザでもFPGA の開発が可能

▮ MATLAB/SimuLink によるSimuLink モデルから、System GeneratorでFPGA のコードを生成することが可能

▮ SimuLinkモデル上でシミュレーションを行うことができるため、動作テストが容易になる

FPGA開発手法(IP Integrator)

-

▮ Xilinx社のVivado統合開発環境に含まれているIPインテグレータというブロックベースの開発手法

▮ IPインテグレータをサポートしたFPGAデザインキットを利用することで、ユーザはブロック図でのモデルベースデザインが可能

▮ PENTEK社のNavigator FDKはIPインテグレータをサポートしている