概要

PicoDigitizer 125は、125MHz 14bit のA/Dを搭載した多チャンネルのSDR無線信号処理装置です。

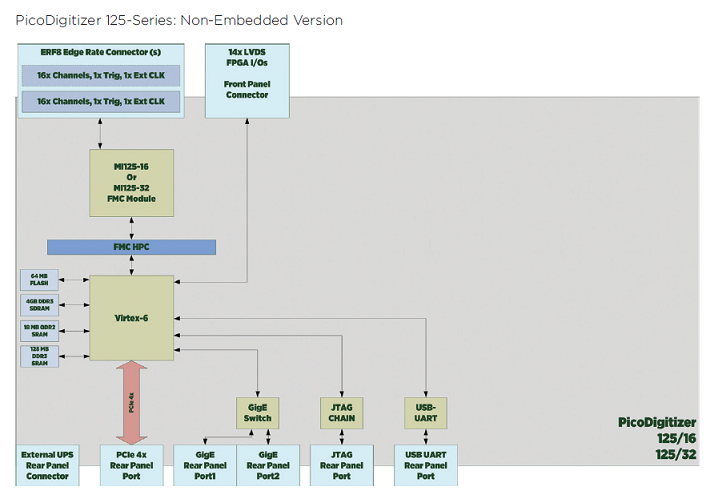

ハーフラックサイズに、A/D & FPGA を組み込んでおり、1000Base-T で PC からの制御が可能です。入力チャンネルは 16/32ch を選択することができます。FPGAは Xilinx Virtex-6 を搭載しています。また オプションでCPU ボードを組み込むことができますので、ユニット単体でシステムを完結させることも可能です。FPGA開発は、VHDL記述によるサンプルコード(BSDK)の他、MATLAB/Simulink によるモデルベースデザイン(MBDK)もサポートしており、特に無線信号の研究や研究室での計測用途に最適です。

- 仕様

-

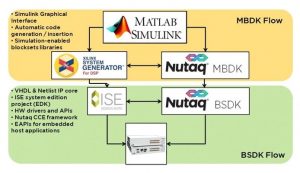

A/Dコンバータ 125MHz, 14bit, 16ch/32ch FPGA 1x Virtex-6 タイプ ボックス - MBDK(モデルベースデザインキット)

▮ MathworksのSimulinkインターフェイスとXilinxのSystem Generatorを組み合わせることにより、VHDL/Verilogの知識がなくてもFPGAイメージを作成できます。

▮ MathworksのSimulinkインターフェイスとXilinxのSystem Generatorを組み合わせることにより、VHDL/Verilogの知識がなくてもFPGAイメージを作成できます。

▮ I/Oインタフェースのプログラミング、FPGA制約の調整、ドライバーのデバッグなど、お客様が付加価値の低いタスクに費やす時間を大幅に削減します。

▮ ホストシミュレーションツールを提供し、シミュレーション内での実際のI/O統合、ステップバイステップのFPGAファブリックデザインの移行、FPGAからホストへの簡単な相互作用、データロギングなどを可能にします。

▮ 記録/再生、ホストI/O制御、データストリーミングライブラリなどのツールを提供します。

- ソフトウェア無線のソリューションプロバイダ

Nutaq社は、1983年にカナダのQuebecに設立されたワイヤレス、スマートビジョン、科学および防衛市場向けのデジタル信号処理ボード、システムおよび設計サービスを提供するソフトウェア無線システムのマーケットリーダーです。

Nutaq社は、1983年にカナダのQuebecに設立されたワイヤレス、スマートビジョン、科学および防衛市場向けのデジタル信号処理ボード、システムおよび設計サービスを提供するソフトウェア無線システムのマーケットリーダーです。

高度に洗練されたデジタル信号処理ボードとシステムを幅広く提供し、完全な製品(ターンキーシステム) を提供します。ソフトウェア無線 (SDR)、5G Massive MIMO、CRAN、HetNet、IoTなど次世代のワイヤレス規格と科学および防衛市場向けのパッシブレーダーや医療用画像処理など、さまざまな分野でイノベーションを促進しています。何十年にもわたるデジタル信号処理 (DSP) の専門知識を活用して、ラピッドプロトタイピング、テスト、および検証ソリューションを開発および提供することで、Nutaq社は5Gの進化に専念するパイオニアとしての地位を確立しています。

ブロック図

スペック

| 入力チャンネル数 | 16ch, 32ch選択可 |

| 出力チャンネル数 (オプション) | 8ch, 16ch |

| サンプリング周波数 | ADC: 125MSPS, DAC: 1000MSPS (オプション) |

| 分解能 | ADC: 14bit, DAC: 16bit (オプション) |

| FPGA | Xilinx Virtex-6 x1 又は x2 |

| ホストI/F | GigE, PCIe-4x |

| CPU (オプション) | Intel Core i7 2715QE |

| ストレージ (オプション) | 64GB SSD, SATA |