背景:

市販の(COTS)ソフトウェア無線機(SDR)製品は、その高い性能と設計の柔軟性により、軍用レーダおよび通信アプリケーションに広く利用されてきました。最新のSDR製品は、統合されたI/O、ARMプロセッサ、およびデジタルデータへのアクセス、ルーティング、信号処理のためのIPを含む大規模FPGAを備えたソリューションを提供します。これらの特性と優れた信号品質、位相コヒーレントサンプリング、およびマルチチャンネルトランシーバを組み合わせたCOTS SDRシステムは、5G開発プラットフォームに最適です。

この記事は、5G製品の市場投入時間を短縮することができる多目的COTSプラットフォームで、Software Defined Radioについて理解していただくことを目的としています。

COTSの歴史:

1990年代初頭、議会の支出削減により、米軍は研究開発費を削減しなければならなかったが、アメリカの安全保障のために世界的な技術的リーダーシップを維持する必要がありました。1994年、当時の国防長官、ウィリアムペリーは、軍のコマーシャル品の購入とコマーシャル仕様の使用を増やすことを要求するメモを書きました。このメモは、1994年の連邦取得合理化法(FASA)の一部として正式に法律に制定されたものであり、汎用的な商用製品の購入を禁止していた過去の厳しい軍事仕様要件からの離脱でした。その結果、今日では豊富なCOTS製品が、軍事用と商業用の両方に利用可能な最新の技術と共に利用可能になりました。

定義

この記事の各セクションはハードウェア、ファームウェア、ソフトウェアのサブセクションに分かれています。ハードウェアはコンポーネントを含むSDR PCBです。ファームウェアは、ロジックデザインを作成しデジタル信号処理(DSP)機能を実装するために使用される内部FPGAコードです。ソフトウェアは、FPGAを制御し追加のDSP機能を実行するためのCコードです。

ハードウェア:

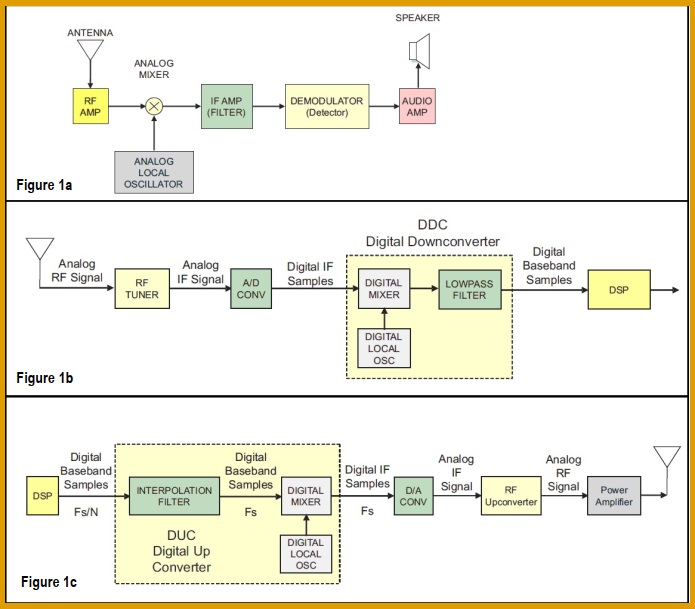

SDRは、RFフィルタ、アナログダウンコンバータ(Lo + Mixer)、バンドパスフィルタ、復調器で構成されていた従来のアナログシステムに代わるものです(Figure 1aを参照)。これらのアナログシステムは、AMまたはFMラジオのような特定のプラットフォームに限定されており、別のプラットフォームが必要な場合は交換する必要がありました。SDRの主な機能は、デジタル信号処理技術を活用して今日の無線トラフィックの複雑さ、精度、帯域幅をサポートすることです。受信機能および送信機能の両方について、アンテナ信号とDSP動作との間で適切なデータ変換が必要とされます。SDRレシーバは、アンテナからのRF信号をA/D変換器でデジタルサンプルに変換し、後続のDSP操作を使用して信号から必要な情報を抽出します(Figure 1bを参照)。SDRトランスミッタは、送信されるデジタル情報を受け取り、必要なDSP操作を実行してD/Aコンバータ用のデジタルサンプルを生成します。そのアナログ出力信号はPAに送られてアンテナに配信されます(Figure 1cを参照)。これらの無線はソフトウェアで定義されているため、マイクロ秒単位で新しいパラメータをオンザフライでプログラムすることも、内部または外部メモリから新しいファームウェアイメージをロードするだけでさまざまな目的に合わせて再設定することもできます。

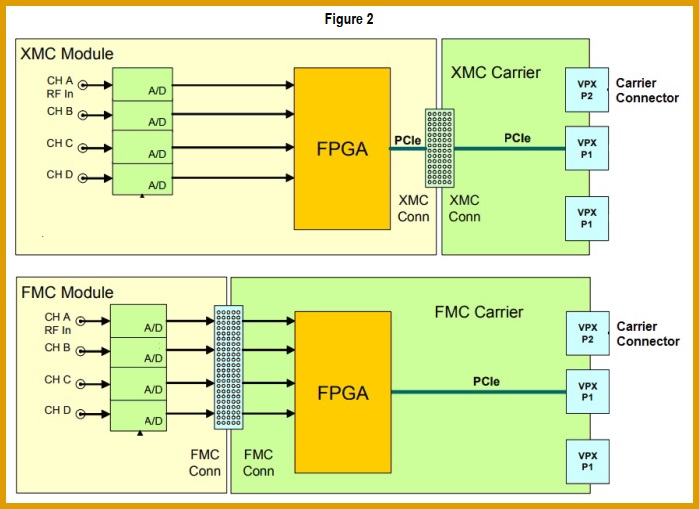

SDRは、優れた信号品質と正確なタイミングのために設計された特殊なPCBボードに実装されます。これらカードの最新世代は、スイッチファブリックメザニンカード(XMC)、またはFPGAメザニンカード(FMC)です。Figure 2は、XMCメザニンがFPGAを含み、FMCがFPGAを搭載したより複雑なキャリアを必要とするという違いがある両方のカードタイプを示しています。この例では、各カードは3U VPXシャーシに収まる3U OpenVPXキャリアに接続されています。

これらのメザニンカードのどちらも、異なるフォームファクタキャリアと組み合わせて、異なるシャーシまたはPCのマザーボードに取り付けることができます。これにより、同じソフトウェア無線機能を複数のシステムの異なるプラットフォームで使用できます。

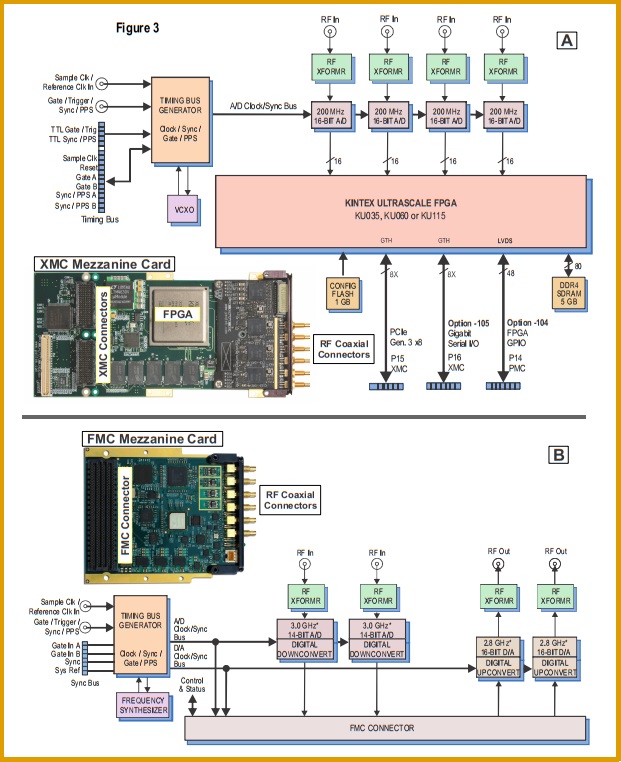

Figure 3に、XMCおよびFMCメザニンカードのイメージと、それに対応する機能ブロック図を示します。ブロック図Aは4chの200MHz A/Dを搭載したXMCカード「Model 71861」で、ブロック図Bは2chの3.0 GHz A/Dと2chの2.8 GHz D/Aを搭載したFMCカード「Model 3320」です。これらのカードは多種多様なマルチチャネルSDRメザニンカードのほんの一例です。XMCカードにはアナログI/OとFPGAの両方が含まれています。

XMCボードの核となるのは、オンボードVCXOまたはリファレンス入力信号を使用する可変サンプリング用のマルチビット周波数シンセサイザを備えた高精度タイミングシステムです(Figure 3参照)。このタイミングシステムは通常、レーダまたはセルラーシステムの非常に正確なタイミング要件のために、NTP(Network Time Protocol)サーバーまたはGPS受信機からの外部同期信号を受け取ります。この精度レベルは、A/Dの位相コヒーレント、FPGA DSPデータ同期、およびD/A信号送信にも必要です。

各A/Dは、100 MHzのナイキスト帯域幅を取得できる最大200 MSPSのサンプリングレートをサポートしています。デジタル無線の一般的な技術は、信号をアンダーサンプリングすることによって、チャネル情報または中間周波数(IF)帯域幅を取得することです。複数のナイキストゾーンを使用する「ファンフォールド」の概念については、以下「ナイキストゾーン・サンプリング」を参照してください。アンダーサンプリングは、低いサンプルレートと高いダイナミックレンジを持つA/Dを使用して、情報を失うことなくより高周波の狭い帯域幅の信号を取得することを可能にします。これが正しく機能するためには、RF入力経路とA/Dがこの高周波の信号に対応する必要があります。前述の200 MHz A/Dの例では、4つ目を除くすべてのナイキストゾーンからのノイズと高調波を低減するために、400 MHzを超える通過帯域と適切なバンドパスフィルタリング(BPF)を持つACトランスが必要です。A/Dサンプリングのナイキスト基準を満たした後、次の段階は通常DDC(デジタルダウンコンバータ)です。DDCは多くの場合、FPGA内のIPファームウェアとして実装されています。これは、周波数変換と帯域幅削減を実行します。

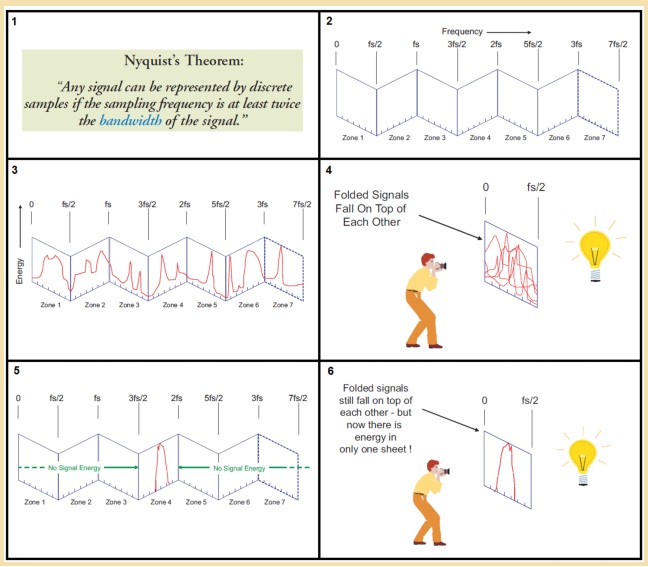

| ナイキストゾーン・サンプリング (次図を参照)

1.アンダーサンプリングの概念を説明する際、周波数と区別するために以下のナイキスト定理で「帯域幅」を強調表示しています。 2.図のファンフォールド用紙は、「ナイキストゾーン」の位置を示しており、これはサンプリング周波数(fs)の1/2の幅をナイキストゾーンとして定義します。XMCボードの例では、fs = 200 MHz、fs/2 = 100 MHzなので100 MHzごとにナイキストゾーンを折り返します。 3.すべての信号エネルギーは、ナイキスト定理の帯域幅要件と周波数要件の両方を満たすために、1つのナイキストゾーンに収まる必要があります。この広帯域信号の例(赤で表示)は複数のゾーンをまたいでいるため「シングルゾーン」のルールに違反しています。 4.この信号をサンプリングした結果を示すために、ファンフォールド用紙を折りたたんでバックライトを当てると、 fs/2を超えるすべての信号エネルギーが最初のゾーンに表示されます。これは、LPFを使用してfs/2を超えるすべての信号エネルギーを除去することで補正できます。 5.もう1つの例は、ナイキストゾーン4(この例では300 MHzから400 MHzの間)に完全に収まる狭帯域信号です。この信号は、他のすべてのゾーンから信号エネルギーを除去する適切なバンドパスフィルタを使用することで正しくサンプリングできます。 6.信号周波数がfs/2以上であるにもかかわらず、信号エネルギーは1つのゾーン内に含まれているためナイキスト定理を満たしています。Zone 1より上のサンプリングは「アンダーサンプリング」と呼ばれます。 |

| ナイキストの定理:

サンプリング周波数が信号の帯域幅の少なくとも2倍であれば、どんな信号でも離散サンプルで表すことができる。 |

ファームウェア:

FPGAは、ロジック・演算器・信号処理のビルディングブロックで構成されており、動作するためにはファームウェア(IP)でコンフィグレーションする必要があります。これはプログラミングの柔軟性に理想的ですが、ファームウェアの開発が必要なため複雑となります。一部のCOTS SDRベンダは、開発プロセスを簡素化するためにボードの基本動作用にFPGA IPを提供しています。これには通常、データ取得・送信するためのアナログ・デジタルI/O機能、およびデータをシステムに転送するためのエンジン、DDC・フィルタ・チャネライザなどの特定の無線機能用のDSP IPが含まれます。

DDC機能には、NCOローカルオシレータ、複合ミキサ、および従来のアナログ無線システムの機能を置き換えるためのデジタルフィルタの3つのIP構成ブロックが必要です(Figure 1aおよび1bを参照)。Figure 1bは、DDCを有するSDRの機能ブロック図です。このDDCで対象となる周波数をベースバンドに変換するために複雑なデジタルミキサーを使用します。ダイレクトデジタルシンセサイザ(DDS)数値制御発振器(NCO)によって駆動される乗算器のペアにより、ユーザは希望の周波数に「チューニング」することができます。次に、ローパスFIRフィルタを通過して、信号をチャネル帯域幅にデシメート(間引き)します。

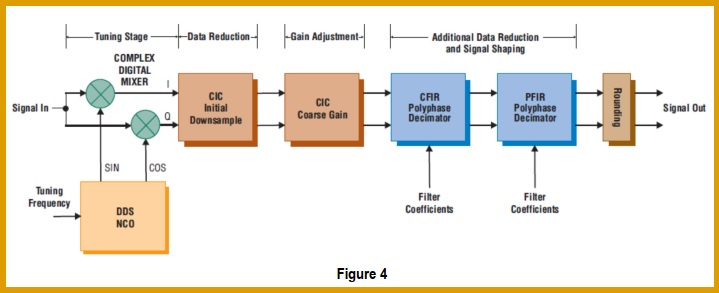

Figure 4は、DDCブロックを詳細に表したもので、細かい間引きとゲイン調整の段階があります。CICフィルタはデータを間引きし、サンプルレートと有効帯域幅を低減します。2段目のCICは更に帯域幅を狭めてコースゲインを調整し、2つのポリフェイズフィルタは最終的な帯域幅を削減し、追加の間引きおよび信号整形を行います。

CFIR(補償FIR)は通過帯域を平坦化するのに役立ち、PFIR(プログラムマブルFIR)はリップルを除去するのに役立ちます。これで、コンプレックスI&QデータをFPGAに転送して演算処理しシステムに転送します。

DDCの2つの主な利点は、間引きの結果としてS/N比が高くなることと、中心周波数を狭帯域信号に同調できることです。信号を間引くとサンプルレートが実質的に低下し、プロセスゲインと呼ばれる無相関のホワイトノイズが減少します。そしてNCOは単一のナイキストゾーン内の特定の搬送波周波数にデジタル的に同調します。

| SNRとデジタルプロセスゲイン

A/DのSN比の計算: SNR = 6.02 * N(bits) + 1.76 dB 例: 200 MHz 16-bit A/Dの場合、SNR = 6.02 * 16 + 1.76 dB = 98 dB A/Dの非線形性、LNA入力からのノイズ、サンプリングクロックのジッタにより高品質のA/Dに対して実測されたSNRは約75 dBに制限されます。この計算では、入力信号がフルスケールであると仮定していますが、これは、ゲインの減少、または高いクレストファクターの通信信号を補正するためのフロントエンドLNAのバックオフ設定のためにしばしば変化します。ダイナミックレンジは、DDCを使用して全ナイキスト帯域幅を目的のチャネル帯域幅まで減らすことで改善できます。 Fs/2 = 100MHzのPentek社の200MHz A/D、および5MHz LTEチャンネルの例では、以下の計算されたプロセスゲイン、またはRMSノイズが低減します: SNRpg = SNR nyquist + 10*log10(Fs/2/ Ffilter) = 75dB + 10*log10(100 MHz/5 MHz) ≒88 dB このように13 dBの改善が期待できます。 |

ソフトウェア:

アプリケーションによっては、ベンダの提供するFPGA IPがアプリケーションの仕様を満たすことがありますが、無線器を操作するには制御ソフトウェアが必要です。FPGA IPは、ソフトウェアプログラムからシステムインタフェースを介して送信される動作パラメータを必要とします。これは通常、WindowsまたはLinuxオペレーティングシステム環境用の「C」呼び出し可能ルーチンとして書かれたボードサポートパッケージ(BSP)の機能です。BSPには、ボード機能をテストするために実行できるライブラリ関数とコンパイル済みのサンプルコードが含まれています。

SDRの例として、DDCでさらに処理するためにA/DにデータをキャプチャしてFPGAに転送するように命令することが挙げられます。この処理されたデータは、メモリに記憶されるかまたはアナログ信号に変換して送信するためにD/Aセクションに転送することができます。これは、BSPソフトウェアライブラリの機能とドライバを使用して開発されたソフトウェアプログラムの例です。ユーザが新しいFPGA IPを作成した場合は、BSPパッケージに含めるために追加の制御ソフトウェアを作成する必要があります。

最新のCOTS SDRテクノロジ

ハードウェア:

過去10年間で、ザイリンクスのようなFPGAメーカーは、シリコン製造プロセスを微細化することによってテクノロジを向上させ、その結果、デバイスサイズ、重量、電力(SWaP)の値を低減しました。2008年後半、ザイリンクスVirtex-6ファミリは40nmプロセスを使用して構築され、FPGAあたり平均2000個のDSPスライスを実装していました。2017年までにUltrascaleファミリは20nmプロセスを使用し、FPGA DSPスライスは約5500個に増加しました。ザイリンクスが提供する最新のSystem-on Chip(SoC)デバイスであるRFSoCは、ARMプロセッサを搭載したFPGAファブリック、A/D、D/Aをすべて同一チップ上に搭載したものです。16nmテクノロジには、4200個以上のDSPスライス、4つの1.5 GHz A53 ARMプロセッサ、2つの600 MHz R5 ARMプロセッサ、8つの4 GHz、12ビットA/D、8つの6.4 GHz、14ビットD/Aが実装されています。

過去10年間で、ザイリンクスのようなFPGAメーカーは、シリコン製造プロセスを微細化することによってテクノロジを向上させ、その結果、デバイスサイズ、重量、電力(SWaP)の値を低減しました。2008年後半、ザイリンクスVirtex-6ファミリは40nmプロセスを使用して構築され、FPGAあたり平均2000個のDSPスライスを実装していました。2017年までにUltrascaleファミリは20nmプロセスを使用し、FPGA DSPスライスは約5500個に増加しました。ザイリンクスが提供する最新のSystem-on Chip(SoC)デバイスであるRFSoCは、ARMプロセッサを搭載したFPGAファブリック、A/D、D/Aをすべて同一チップ上に搭載したものです。16nmテクノロジには、4200個以上のDSPスライス、4つの1.5 GHz A53 ARMプロセッサ、2つの600 MHz R5 ARMプロセッサ、8つの4 GHz、12ビットA/D、8つの6.4 GHz、14ビットD/Aが実装されています。

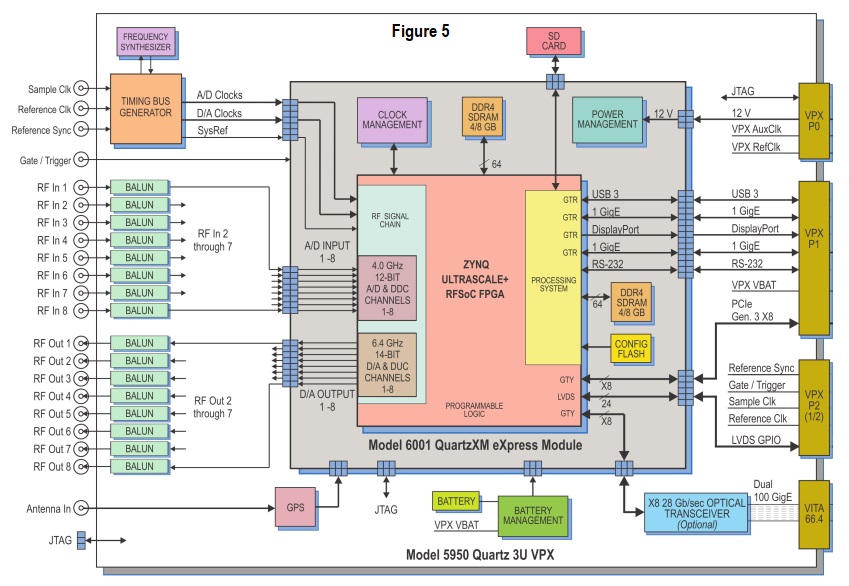

この革新的な技術は、5G無線製品を開発するエンジニアにマルチチャンネルSDRトランシーバーを提供するためにCOTS製造業者によって使用されています。Figure 5は、ザイリンクスRFSoCの機能ブロック図で、Pentekの「Model 5950」 3U VPXボードの中心的なコンポーネントです。グレーの部分は、3U VPXキャリアに搭載する為、完全にコネクタ接続されたRFSoCシステムオンモジュール(SOM)です。このデバイスは、前世代のFPGAと同様にギガビットイーサネットポートを介して制御できますが、オンボードARMプロセッサを使用すると、自律的な操作、またはローカルまたは外部ネットワーク経由で通信・制御できます。

ファームウェア:

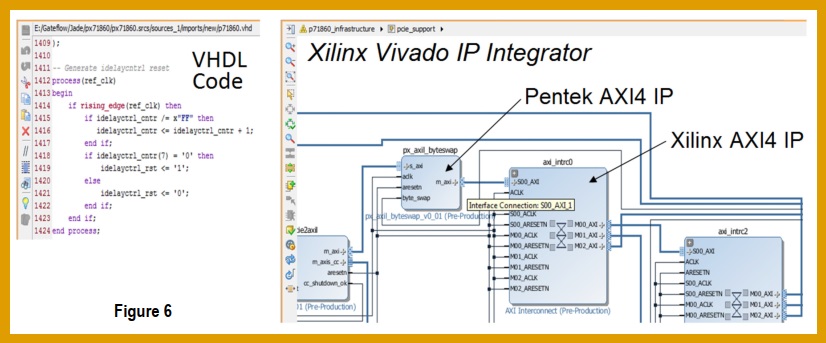

前世代のFPGAは、VeriLog、またはVHDLなどのテキスト形式のハードウェア記述言語(HDL)を使用してプログラムされていました。最新のAXI4準拠のIPブロックは、ザイリンクスのVivadoに含まれています。ザイリンクスのIPインテグレーターツールには、HDLコードを表す仮想グラフィカルブロックがあり、ドラッグアンドドロップで相互に接続できます。

Figure 6は、右側にグラフィックブロック表現と、左側にVHDLコード記述を示しています。この直感的なプログラミング方法により、FPGAに不慣れな人でも、FIRフィルタやDDCなどのハードウェアを表す論理ブロックを使用してSDRを作成できます。このプログラミング方法で、ベンダ提供のハードウェア固有のIPブロックとザイリンクスのメインライブラリのIPブロックを迅速に統合できます。

ソフトウェア:

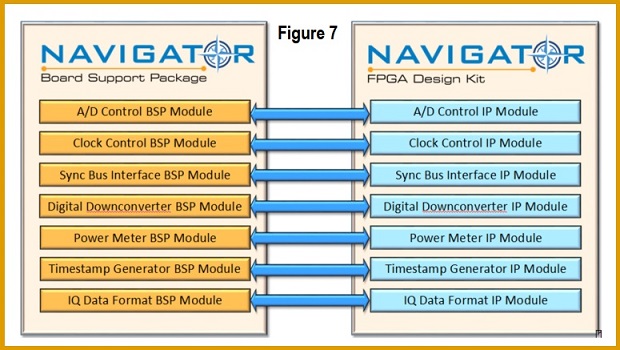

これら最新のIPプログラミングの進歩により、COTSベンダは関連するすべてのIPモジュールとBSPモジュールを一緒に提供することができました。Figure 7は、各IPモジュールが関連するFPGAプログラムパラメータを含む単一の対応するBSPモジュールを持っている様子を示しています。Figure 7は、Pentek Navigator BSPおよびNavigator FDK IPモジュールのリスト例を示しています。

5Gアプリケーションの具体例:

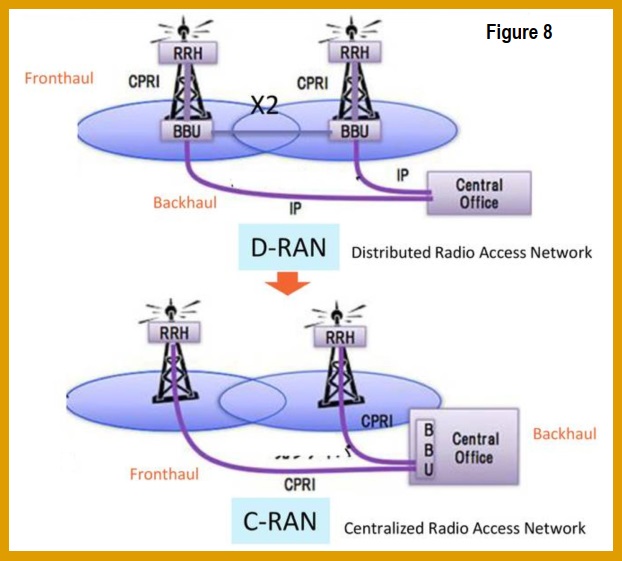

Figure 8は、分散型無線エリアネットワークと集中型無線エリアネットワークの違いを示しています。従来のD-RANの基地局は、新しいC-RANに置き換えられています。最初は同軸ケーブルを光ファイバに置き換えて信号品質を確保し、回線交換からIPパケット交換にかけて音声とデータを1つのシステムに統合しました。最新の5Gミリ波およびMassiveMIMOアプリケーションでも、このネットワークと無線の分離が必要です。

Figure 8は、分散型無線エリアネットワークと集中型無線エリアネットワークの違いを示しています。従来のD-RANの基地局は、新しいC-RANに置き換えられています。最初は同軸ケーブルを光ファイバに置き換えて信号品質を確保し、回線交換からIPパケット交換にかけて音声とデータを1つのシステムに統合しました。最新の5Gミリ波およびMassiveMIMOアプリケーションでも、このネットワークと無線の分離が必要です。

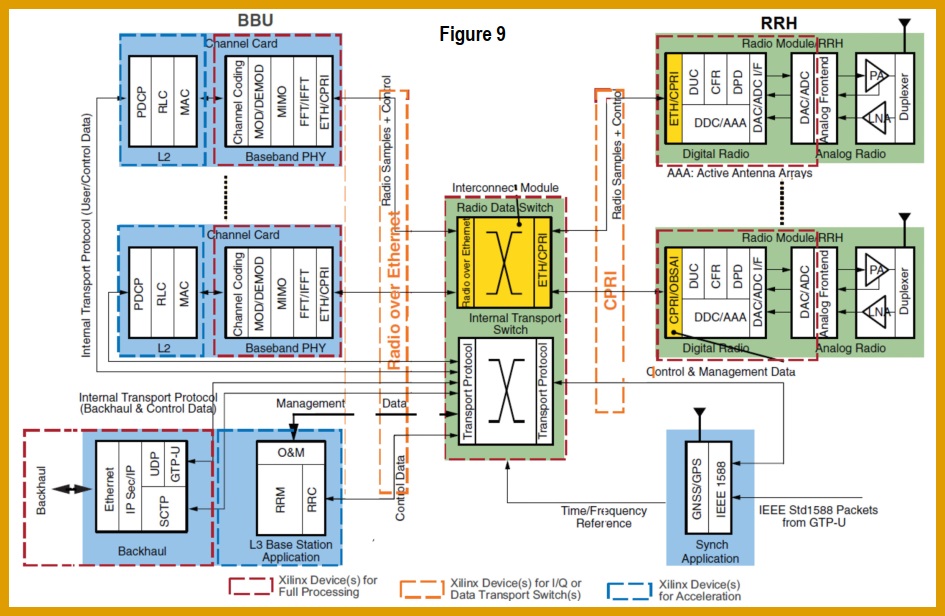

Figure 9は、ベースバンドユニット(BBU)、リモートレディオヘッド(RRH)、GPS時間および周波数リファレンス、および無線基地局からなる集中無線エリアネットワーク(C-RAN)、相互接続スイッチの機能ブロック図です。BBUは通常バックオフィスのために複数の光データラインにアクセスする中央局または仮想ネットワーク(クラウド)にあり、RRHはエンドユーザにより近い外部の場所にあります。BBUとRRHは、システム要件に応じて、Common-Public-Radio-Interface(CPRI)、Open-Base-Station-Architecture-Initiative(OBSAI)を使用して接続できます。レガシーセルラー、5G TF(Verizon仕様)、または3GPP 5G NR仕様と組み合わせたこれらのさまざまな転送モードオプションを組み合わせて、複雑な異種ネットワークを形成することができます。テストを必要とする多くのソリューションのため、利用可能な多数のマルチチャンネルバージョンからCOTS SDRプラットフォームを選択することは価値があります。Figure 9は、RRHをエミュレートするために使用されるCOTS SDRボードの例です。

ハードウェア:

ユーザ機器で、OTA信号はRRH内のアンテナを介してLNAによって受信されます。このRF信号は、A/Dに入力される前にフィルタリングされゲイン調整されます。A/Dからのデジタル化されたI/Qサンプルデータは、デジタルラジオでパケット化され、無線データスイッチを介してBBUにフロントホールで転送されます。パケット化されたデータは、FFT、MIMOアルゴリズム、復調、チャネル符号化のためにビットストリームに変換されます。次にこのデータは内部トランスポートスイッチによって管理され、識別およびさらなる処理のためにメインセルラネットワークへのバックホールトランスポートのために再パケット化されます。通話が進行中の場合は、逆のプロセスで相手方にOTAを送信するため、ユーザーデータがCPRIまたはイーサネット上のイーサネットプロトコルを使用して別のRRHに送信されます。

前の説明は、このプロセスを単純化したものです。

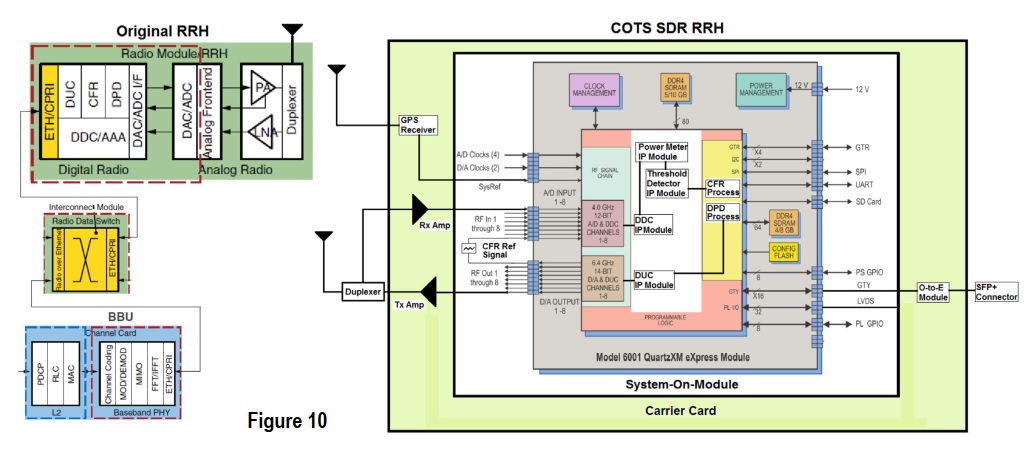

Figure 10は、左側にRRH、無線データスイッチ、BBUを、右側にCOTS SDR RRHを示した最初のC-RANの一部です。カスタムモジュラキャリアカード(薄緑色の領域)には、RXおよびTX増幅器、GPS受信機、O/Eトランシーバモジュールが含まれています。SOM(グレーの領域)には、RFSoC、電力管理、データ保存、アナログおよびデジタルI/O用のすべての接続が含まれています。アンテナからの着信RF信号はデュプレクサを介してRX LNAに接続されハイパワーアンプ(PA)の送信レベルから分離して、A/Dチャネルに接続されます。このSOMとカスタムキャリアの組み合わせは、次のセクションで説明するIPにより元のRRHをエミュレートできます。

ファームウェア:

FPGAファブリック内に入ると、デジタルサンプルは間引き、周波数選択、調整されDDCでフィルタリングされます。DDC出力サンプルは測定のために電力計モジュールにストリーミングされ、そしてしきい値検出器IPモジュールにおいて分類されます。これら処理されたサンプルは、クレストファクタ低減およびデジタルプリディストーションルーチンのためにARMプロセッサにストリーミングされてから、再送信のためにDUCでアップコンバートされます。DUCはDDCの逆で、間引きの代わりに周波数変換と補間を実行します。デジタル化されたI/Qサンプルデータは、前述のように無線データスイッチを介してBBUに転送するためにデジタル無線機でパケット化されます。さまざまなチャネルとさまざまなデータ転送プロトコルがあるため、信号の最大データスループットを計算する必要があります。

| 最大データ転送要件 例1

2本のアンテナと5 MHzのLTEチャネル帯域幅を持つリモートRRHには、次のデータ転送要件があります。 ● 5 MHzチャネルでは、情報をキャプチャするために少なくとも10 MHzのサンプリング、または10 MSPSが必要です。 16ビットサンプルあたり2バイト、およびIとQ用に2サンプルあります。 ● SRmax = 5MS/s ×2Byte/s×2(I&Q) = 20Mbyte/s×8bit/Byte = 160Mb/s ● アンテナが2本あるため、160 Mbps/2 = 320 Mbpsのデータスループットが必要で、10~25 GbpsのCPRIポートでは問題ありません。 |

| 最大データ転送要件 例2

100 MHzのチャンネルと8つのアンテナ入力を備えた新しい5Gリンクは、データ転送要件を高めます。 複数のCPRIポートに必要とされるのは52 Gb /s。上記の計算では、エンコードのバリエーションは無視されます。 |

ソフトウェア:

必要な制御レベルに応じて、新しいIPおよびARMプロセッサ用にBSPルーチンを作成する必要があります。または、FPGAと連携してARMプロセッサを自律的に動作するようにプログラムすることができます。

まとめ:

この記事の目的は、5G開発プラットフォームに使用するSDRシステムを作成するために、COTSベンダから入手可能な最新のハードウェア、ファームウェア、ソフトウェア、および設計ツールについて従来の無線技術者に慣れ親しんでもらうことでした。これらのSDRプラットフォームは、絶えず変化する5G設計要件に準拠する優れたシグナルインテグリティ性能、高いテスト再現性、およびモジュール式アセンブリを提供します。将来の5Gインプリメンテーションは実験のための多くの開発プラットフォームを必要とするため、この出発点としてCOTSシステムの使用は製品化期間の加速を確実にするでしょう。

—————————————————————–

原文ドキュメント:Pentek社

PIPE281.pdf

Accelerating 5G Product Development by Using a COTS-Based SDR System for the Development Platform

関連製品

Model 6001:4GHz A/D & 6.4GHz D/A 搭載 Zynq UltraScale+ RFSoC FPGAボード (小型モジュール)

Model 7050:4GHz A/D & 6.4GHz D/A 搭載 Zynq UltraScale+ RFSoC FPGAボード (PCIe)

Pentek社について

Pentek社は、ISO 9001:2015認定企業として、デジタル信号処理・ソフトウェア無線・データ収集用の組込みコンピュータボードおよびレコーディングシステムを設計・製造しています。製品には、商用環境と耐環境の両方に対応したAMC、XMC、FMC、PMC、cPCI、PCIe、VPXのフォームファクタで準備されており、レーダ、無線通信、SIGINT、ビームフォーミング等の用途に幅広く利用されています。Pentek社の詳細については、www.pentek.comをご参照ください。