A/D & D/A 搭載 FPGAボードModel 5950

4GHz A/D & 6.4GHz D/A 搭載 Zynq UltraScale+ RFSoC FPGAボード (VPX)

概要

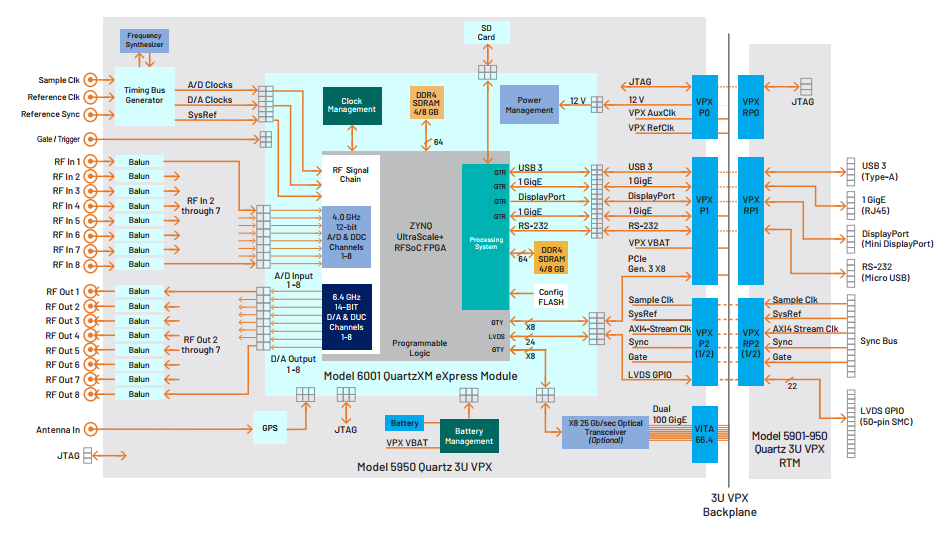

Model 5950は、Zynq UltraScale+ RFSoC (4GHz AD & 6.4GHz DA内蔵) を搭載した 3U VPXタイプの FPGAボードです。

FPGA内に4.0GHz 12bit 8ch ADコンバータと6.4GHz 14bit 8ch DAコンバータを内蔵しています。更に、FPGA内にはARMプロセッサを内蔵していますので、1ボードで送受信機を構築することが可能となります。オンボードメモリに4GB DDR4 SDRAMを搭載しており、ホストインタフェースは、PCIe Gen.3 x8レーンで高速データ転送が可能です。

5G無線通信、気象レーダ、合成開口レーダ、パルスレーダ、フェーズドアレイレーダ、デジタルビームフォーミング、無線通信、ターゲット認識等の高速デジタル信号処理向けアプリケーションに最適です。

- 仕様

-

A/Dコンバータ 4GHz, 12bit, 8ch D/Aコンバータ 6.4GHz, 14bit, 8ch FPGA 1x Zynq UltraScale+ RFSoC ドライバ Linux タイプ 3U VPX 温度範囲 -40 ~ +70℃ (*Conduction Cool) - 特徴

- ▮ Xilinx Zynq UltraScale+ RFSoC FPGAを搭載

- ▮ 4GHz 12bit ADC及び6.4GHz 14bit DACを内蔵

▮ 16GBのDDR4オンボードSDRAM

▮ オンボードGPSレシーバ

▮ PCI Express x8 (Gen. 1/2/3) インターフェース

▮ カスタムI/OのためのFPGAへのLVDS接続オプション

▮ Gigabitシリアル通信用のVITA-66.4光インターフェイスオプション

▮ デュアル100GigE UDPインターフェイス

▮ VITA-46, VITA-48, VITA-66.4, VITA-57.4, VITA-65 (OpenVPX) などVITA規格と互換

▮ QuartzXM eXpressモジュールにより他のフォームファクタへの移行が可能

▮ Model 8257 1スロット3U VPX開発用シャーシ

▮ 「Model 6001」のカスタムキャリアを設計するためのModel 4801キャリアデザインキットオプション

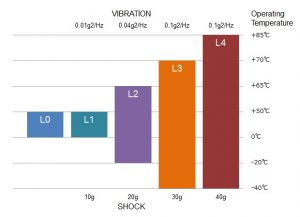

▮ 100Gbイーサネットデータレコーダ「Model RTR 2757」(オプション) - ▮ Pentek社の耐環境仕様レベル

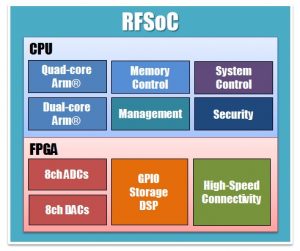

- RFSoCとは

RFSoCとはRF System On Chipの略で、8ch A/D及び8ch D/AとArm CPUコアを内蔵したXilinxのFPGAデバイスです。Zynq UltraScale+のシリーズで、以前のシリーズZynq UltraScale+ MPSoCをベースにしています。MPSoCは、UltraScale+プログラマブルロジックに統合された最大4つのARM Cortex-A53アプリケーションプロセッサと2つのARM Cortex-R5リアルタイムプロセッサを含む、システムオンチップ(SoC)アーキテクチャです。このソリューションは、1つのICにFPGAのハードウェアプログラマビリティとプロセッサのソフトウェアプログラマビリティの柔軟性を提供します。

RFSoCとはRF System On Chipの略で、8ch A/D及び8ch D/AとArm CPUコアを内蔵したXilinxのFPGAデバイスです。Zynq UltraScale+のシリーズで、以前のシリーズZynq UltraScale+ MPSoCをベースにしています。MPSoCは、UltraScale+プログラマブルロジックに統合された最大4つのARM Cortex-A53アプリケーションプロセッサと2つのARM Cortex-R5リアルタイムプロセッサを含む、システムオンチップ(SoC)アーキテクチャです。このソリューションは、1つのICにFPGAのハードウェアプログラマビリティとプロセッサのソフトウェアプログラマビリティの柔軟性を提供します。

RFSoCはMPSoC基盤の上に構築され、プログラマブルデジタルダウンコンバータ(DDC)を装備した8chの4 GSPS 12ビットA/Dコンバータと、デジタルアップコンバータ(DUC)を装備した8chの6.4 GSPS 14ビットD/Aコンバータを内蔵しています。

- 開発用のVPXシャーシをご用意しています

Model 5950専用の開発用VPXシャーシをご用意しています。フロント側にModel 5950用のスロットが1スロットあり、リア側にRTM(リアトランジションモジュール)を搭載します。RTMにはJTAGポート、COMポート、LANポートがありユーザの開発用PCと接続することができます。

Model 5950専用の開発用VPXシャーシをご用意しています。フロント側にModel 5950用のスロットが1スロットあり、リア側にRTM(リアトランジションモジュール)を搭載します。RTMにはJTAGポート、COMポート、LANポートがありユーザの開発用PCと接続することができます。

- Model 5903 高速シンクロナイザボード

Model 5903 高速シンクロナイザボードは、システム内の複数のModel 5950ボードを同期することができます。これにより、5950ボードを拡張して更に多チャンネルの高速データ収集アプリケーションの同期サンプリングが可能になります。オンボードのプログラムマブルクロックジェネレータにより、サンプリングクロックを生成します。最大8枚のModel 5950ボードを同期することができ、各ボードはトリガー、ゲーティング機能に使用できるタイミング信号とともに共通の同期用クロックを受信します。

Model 5903 高速シンクロナイザボードは、システム内の複数のModel 5950ボードを同期することができます。これにより、5950ボードを拡張して更に多チャンネルの高速データ収集アプリケーションの同期サンプリングが可能になります。オンボードのプログラムマブルクロックジェネレータにより、サンプリングクロックを生成します。最大8枚のModel 5950ボードを同期することができ、各ボードはトリガー、ゲーティング機能に使用できるタイミング信号とともに共通の同期用クロックを受信します。

Model 5903には、外部ソースからの信号を入力するための4つのフロントパネルMMCXコネクタがあります。1つはリファレンスクロック用、1つは同期用、2つはゲート/トリガー信号用です。内部プログラマブルクロックジェネレータは、1~5GHzのサンプリングクロック周波数を生成できます。

サンプリングクロックは、オンボードの100 MHzリファレンスにロックするか、外部リファレンスにロックすることができます。同様に、同期およびゲート/トリガーは、ソフトウェアを介してオンボードで生成することも、外部ソースを使用することもできます。- ⇒ 8枚ボード同期システム構成例

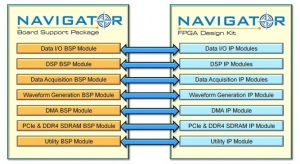

- FPGAデザインキットとボードサポートパッケージ

特殊な機能を必要とするアプリケーションの場合、ユーザーはデータ処理用に独自のカスタムIPをインストールできます。Navigator FPGAデザインキット「Navigator BSP」には、XilinxのVivado®IPIntegratorで編集できるブロックデザインベースのFPGAリファレンスデザインが含まれています。IP Integratorのブロックデザインに加えて、すべてのソースコードと完全なIPコアドキュメントが含まれています。開発者は、独自のIPをリファレンスデザインと統合する、又はNavigator FDKを使用してIPをオリジナルのカスタムIPに完全に置き換えることができます。

特殊な機能を必要とするアプリケーションの場合、ユーザーはデータ処理用に独自のカスタムIPをインストールできます。Navigator FPGAデザインキット「Navigator BSP」には、XilinxのVivado®IPIntegratorで編集できるブロックデザインベースのFPGAリファレンスデザインが含まれています。IP Integratorのブロックデザインに加えて、すべてのソースコードと完全なIPコアドキュメントが含まれています。開発者は、独自のIPをリファレンスデザインと統合する、又はNavigator FDKを使用してIPをオリジナルのカスタムIPに完全に置き換えることができます。

Navigator FDKの関連製品であるNavigatorボードサポートパッケージ「Navigator FDK」は、Model 5950のハードウェアとIPを制御するための完全なC言語ライブラリを提供します。Navigator FDKライブラリとBSPライブラリは相互にミラーリングしており、各IP機能は一致するソフトウェア機能によって制御され、IPとソフトウェア開発の同期を維持する作業を簡素化します。

Navigator BSPには、ARM Cortex-A53プロセッサで実行されるXilinxのPetaLinuxのサポートが含まれています。 PetaLinuxで実行する場合、Navigator BSPライブラリを使用すると、ローカルまたはARMで実行されているアプリケーションから、またはNavigator APIを使用して、リモートシステムコンピュータから制御およびコマンドを実行してModel 5950を完全に制御できます。

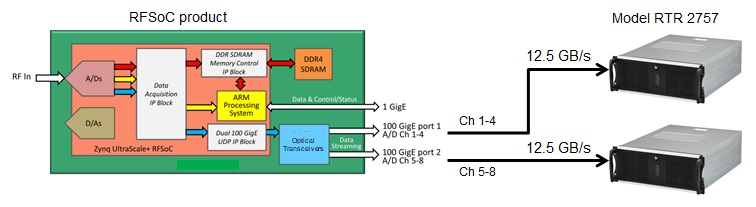

- 100Gigabit Ethernetレコーダ「Model RTR 2757」(オプション)

- Model RTR 2757はModel 5950と接続し、8chのA/Dデジタルデータをリアルタイムに記録することができます。

- ソフトウェア無線のパイオニア

Pentek社は、1986年に米国New Jerseyで設立された高速リアルタイム記録システム、データ取得とI/O、DSP (デジタル信号処理) および SDR (ソフトウェア無線) のリーディングサプライヤです。現在はMercury Systems社のDSP部門としてMercury Systems社の製品ラインナップを拡充しています。

Pentek社は、1986年に米国New Jerseyで設立された高速リアルタイム記録システム、データ取得とI/O、DSP (デジタル信号処理) および SDR (ソフトウェア無線) のリーディングサプライヤです。現在はMercury Systems社のDSP部門としてMercury Systems社の製品ラインナップを拡充しています。

30年以上にわたり、多くのミリタリプログラムや商用市場で顧客の要求を満たすボードとレコーディングシステムを設計および構築しており、ラボ向けおよび耐環境の高性能COTSボードと記録システムソリューションを提供しています。Pentek社の製品は、AMC、cPCI、FMC、PCIe、PMC、XMC、VME、VPX等の各種フォームファクタのボードレベル製品とポータブル、ラックマウント、SFF(スモールフォームファクタ)の記録システムを米国内で設計・製造しています。レーダー、通信、SIGINT、ビームフォーミング、ソフトウェア無線、SATCOM市場向けに広く供給しており、長期的な製品の可用性とライフサイクルサポートを提供します。

- アプリケーション

- AE06:COTSベースのSDRシステムが5G製品開発を加速する

AE19:レーダの原理とそのアプリケーション

AE27:リアルタイム組込みシステム製品を選択するための重要なヒント

AE61:SOSA:組込みミリタリ電子システムの将来の方向性

- Model 5950 デモンストレーションビデオ

- QUARTZファミリ製品概要

ブロック図

スペック

| ▮アナログ入出力 | |

| 入出力レンジ | +4dBm (50Ω) |

| 入出力タイプ | トランスフォーマカップル (Mini-Circuits製TCM1-83X+) |

| コネクタ | MMCX |

| ▮FPGA | |

| 標準 | Xilinx Zynq UltraScale+ RFSoC XCZU27DR |

| オプション | Xilinx Zynq UltraScale+ RFSoC XCZU28DR |

| ▮A/Dコンバータ (FPGAに内蔵) | |

| チャンネル数 | 8ch |

| サンプリングレート | 4.0GHz |

| 分解能 | 12bit |

| ▮DDC (FPGAに内蔵) | |

| チャンネル数 | A/D毎に1ch |

| デシメーション | 1x, 2x, 4x, 8x |

| LOチューニング周波数・分解能 | 48bit, 0 ~ ƒs |

| フィルタ | 80% 通過帯域, 89dB 阻止帯域減衰 |

| ▮D/Aコンバータ (FPGAに内蔵) | |

| チャンネル数 | 8ch |

| サンプリングレート | 6.4GHz |

| 分解能 | 14bit |

| ▮DUC (FPGAに内蔵) | |

| チャンネル数 | D/A毎に1ch |

| インターポレーション | 1x, 2x, 4x, 8x |

| LOチューニング周波数・分解能 | 48bit |

| フィルタ | 80% 通過帯域, 89dB 阻止帯域減衰 |

| ▮プロセッサ(FPGAに内蔵) | |

| ARM Cortex-A53 | 4 core, 1.5GHz |

| ARM Cortex-R5 | 2 core, 600MHz |

| ▮メモリ | |

| タイプ | DDR4 SDRAM |

| サイズ | 4GB (オプション: 8GB) |

| スピード | 1200MHz (2400MHz DDR) |

| ▮ホストインタフェース | |

| PCI Express | Gen.1, 2, 3: x4, x8 |

| ▮ソフトウェアサポート | |

| Linux | |

| ▮環境条件 (標準仕様) | |

| 動作温度 | 0 ~ +50℃ |

| 保存温度 | -20 ~ +90℃ |

| 相対湿度 | 0 ~ 95% *結露なきこと |

| ▮耐環境仕様 | |

| 耐環境仕様レベル | L0 ~ L3 Conduction Cool support |